CPLD je objasnio: Vodič za programibilne logičke uređaje

U dinamičnom svijetu elektroničkog dizajna, složeni programabilni logički uređaji (CPLD) ističu se kao svestrani alati, neprimjetno miješanje prilagodljivosti, preciznosti i učinkovitosti.Ovi uređaji revolucionirali su dizajn kruga uvođenjem programabilnih makro stanica i dominantne matrice međusobno povezivanja, omogućujući stvaranje zamršenih logičkih funkcija s izuzetnom pouzdanošću.Od njihovog osnutka u 1980 -ima do njihove ključne uloge u modernim industrijama poput umrežavanja, automobila i zrakoplovstva, CPLD su dokazali potrebni za traženje i fleksibilnosti i performansi.Ovaj se članak kopa u putovanje CPLD -ovima, njihovim karakterističnim značajkama, praktičnim primjenama i programskim metodologijama koje ih čine kamen temeljac u dizajnu digitalne logike.Katalog

Pregled CPLD -a

Unutar dominacije složenih programabilnih logičkih uređaja (CPLD), otkriva sofisticiranu tapiseriju programabilnih logičkih makro stanica, isprepletene kroz dominantnu matricu međusobnog povezivanja.Ove makro ćelije (MC) i ulazne/izlazne jedinice (I/O) jedinice omogućuju vam vješto dizajniranje krugova, konfigurirajući strukture za jedinstvene funkcije.Za razliku od uređaja koji su zbunjeni njihovim zamršenim vremenom povezivanja, CPLD koriste nepokretne metalne žice.Ova karakteristika daje im dosljedno i predvidivo ponašanje sata, čineći vremenski predviđanja pouzdanijim i preciznijim.

Putovanje i upotreba

1970 -ih najavio je pojavu programabilnih logičkih uređaja (PLDS), potičući pomak prema programibilnim makro jedinicama.Ovaj je pomak uveo veliku fleksibilnost dizajna, izdvajajući ih od statičkih digitalnih krugova, iako je njihova korisnost u početku bila ograničena na jednostavnije krugove.Pojava CPLD-a sredinom 1980-ih revolucionirala je ovaj krajolik, utrčavajući put složenim dizajnom kruga.Od tada su se utkali u tkaninu industrija poput umrežavanja, automobilske elektronike, CNC obrade i zrakoplovnih sustava.Možete se podsjetiti na način na koji CPLD -ovi pojednostavljuju procese koji su jednom zahtijevali pažljivi ručni rad, označavajući izvanredan skok u učinkovitosti.

Karakteristične kvalitete CPLD -a

CPLD se razlikuju svojim prilagodljivim programiranjem, opsežnom integracijom, brzim mogućnostima razvoja i širokom primjenom primjenjivosti, zajedno s ekonomičnim troškovima proizvodnje.Oni se sviđaju onima s minimalnim iskustvom hardvera, koji služe kao pouzdani i sigurni proizvodi koji ne zahtijevaju iscrpno testiranje.Kao svjedočanstvo njihove sposobnosti u velikim dizajnom kruga, CPLD-ovi igraju ključnu ulogu u razvoju prototipa i služe traje ispod 10 000 jedinica, utječući na korisnu kompetenciju za vas.Adeptivnost s kojom se CPLD -ovi prilagođavaju evoluiranim zahtjevima projekta često im donosi uvažavanje, naglašavajući njihovu stvarnu svestranost u dinamičnim okruženjima.

Metode primjene

Ovi integrirani krugovi omogućuju vam da razradite logičke funkcije prilagođene njihovim potrebama koristeći sheme i jezike opisa hardvera na razvojnim platformama.Na primjer, u dizajniranju sekretarice, sheme i opisa hardvera pripremaju se i sastavljaju na računalu.Koristeći kabel za preuzimanje, kôd se prenosi na CPLD za programiranje u sustavu, što sadrži testiranje, rješavanje problema i poboljšanje dizajna.Uspješno izrađeni dizajni tada se masovno proizvode repliciranjem CPLD čipova.U projektima poput sustava semafora, ponavljanje procesa dizajniranja postaje neophodno, slično obnovi kuće kako bi se obnovila njegova novost.Ova ponavljajuća metodologija često postavlja temelje za savladavanje, jačajući i vještine i samopouzdanje.

Vodeće varijante

Kroz godine, tvrtke poput Altera, rešetke i Xilinx predstavile su istaknute linije CPLD -a.Primjeri primjere uključuju Altera EPM7128S, Rešetke LC4128Vi Xilinxov XC95108 .Ovi su modeli pronašli istaknute uloge u različitim globalnim aplikacijama.Oni koji su imali privilegiju raditi s tim različitim proizvodima često primjećuju suptilne, ali snažne razlike koje optimiziraju određene funkcionalnosti.To odražava fini postupak odabira koji utječu određeni zahtjevi projekta, gdje svaka varijanta drži svoju jedinstvenu privlačnost.

Identifikacija i klasifikacija FPGA i CPLD

|

Aspekt |

CPLD |

FPGA |

|

Formiranje logičkog ponašanja |

Oblikujte logičko ponašanje pomoću strukture termina proizvoda.

Primjeri: rešetka ISPLSI serija, Xilinx XC9500 Series, Altera Max7000S

serija, rešetka |

Obradite logičko ponašanje pomoću metode pretraživanja tablice.

Primjeri: Xilinx Spartan Series, Altera Flex10K, ACEX1K serija |

|

Pogodnost |

Pogodno za algoritme i kombinacijsku logiku, djela

bolje s ograničenim okidačima i bogatim izrazima proizvoda |

Pogodno za uzastopnu logiku, bolje funkcionira s

strukture bogate okidačima |

|

Kašnjenje vremena |

Kontinuirana struktura ožičenja pruža jednolično i

Predvidljiva vremenska kašnjenja |

Segmentirana struktura ožičenja dovodi do nepredvidivog vremena

kašnjenje |

|

Programiranje fleksibilnosti |

Fiksni unutarnji krugovi modificirani su za programiranje.

Koristi se programiranje logičkog bloka |

Unutarnje ožičenje je modificirano za programiranje.Logika

Programiranje na razini vrata omogućuje veću fleksibilnost |

|

Integracija |

Niža integracija u usporedbi s FPGA |

Veća integracija s složenijom strukturom ožičenja i

logička implementacija |

|

Jednostavnost upotrebe |

Lakše se koristiti s programiranjem putem E2Proma ili FastFlash -a.

Nije potreban vanjski memorijski čip |

Za pohranjivanje programiranja zahtijeva vanjsku memoriju

Informacije, što dovodi do složenije korištenje |

|

Brzina i predvidljivost |

Brža brzina i bolja predvidljivost vremena zbog

Skinuta međusobna povezanost između logičkih blokova |

Sporija brzina i manje predvidljivo vrijeme zbog

Programiranje i distribuirana povezanost na razini vrata |

|

Tehnologija programiranja |

Koristi E2PROM ili Flash memorijsko programiranje.Programiranje podataka

zadržava se kada se sustav isključi.Podržava programiranje na a

programer ili u sustavu |

Na temelju programiranja SRAM -a.Programiranje podataka se gubi kada

Sustav se isključuje i mora biti ponovno učitan.Podržava dinamiku

konfiguracija |

|

Povjerljivost |

Nudi bolju povjerljivost |

Pruža manju povjerljivost |

|

Potrošnja energije |

Općenito veća potrošnja energije, posebno s

veća integracija |

Niža potrošnja energije u usporedbi s CPLD -om |

Programski jezici CPLD -a

Analiza kako su programirani složeni programabilni logički uređaji (CPLD) kamen temeljac u izradi svestranih hardverskih rješenja.Povijesne metode za programiranje CPLD -a oslanjale su se na dijagrame ljestvica ili jezike opisa hardvera (HDLS), pri čemu su Verilog HDL i VHDL prevladavajući izbora.Odabrani jezik može oblikovati i dizajnersku strategiju i operativnu učinkovitost implementacija.

• Verilog HDL: Verilog HDL njeguje se zbog svoje jednostavne mogućnosti sintakse i robusne simulacije, što odražava metodologije korištene u dizajnu digitalne logike.Njegova integracija s alatima za automatizaciju elektroničkih dizajna (EDA) omogućuje vam neprimjetno provođenje sinteze i simulacije.Primijećeno je da C-slična sintaksa Veriloga snižava barijeru za ulazak za one s programskim pozadinama, ubrzavajući put od dizajna do implementacije u širokom rasponu industrijskih sektora.

• Vhdl: VHDL pruža složeniju i izražajnu opciju za HDL programiranje.Često je izbor za projekte koji zahtijevaju pažljivu dokumentaciju i strogo provjeravanje, osobine koje se procjenjuju u zrakoplovnoj i obrambenoj industriji.Možete napomenuti da, unatoč potencijalnoj složenosti VHDL -a u manjim projektima, njegova disciplinirana struktura podržava stvaranje izuzetno pouzdanih dizajna, nužnost u okruženjima u kojima je sigurnost dominantna.

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

NMOS tranzistori: dizajn, rad i aplikacije

na 2024/12/29

Brza Fourierova transformacija (FFT): Revolucionarizacija digitalne obrade signala

na 2024/12/29

Popularni postovi

-

Složeni računali s uputama: Kako su promijenili računanje?

na 8000/04/18 147760

-

USB-C pinout i značajke

na 2000/04/18 111974

-

Korištenje Xilinx Unified simulacijski primitivi: sveobuhvatni vodič za dizajn i simulaciju FPGA

na 1600/04/18 111351

-

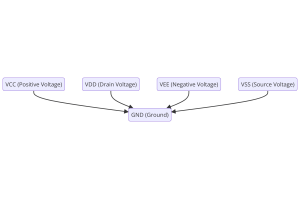

Naponi napajanja u elektronici: Značenje VCC, VDD, VEE, VSS i GND

na 0400/04/18 83742

-

RJ45 Vodič za priključak: pinout, ožičenje, vrste kabela i upotreba

na 1970/01/1 79527

-

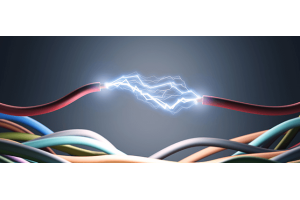

Krajnji vodič za kodove u boji žice u modernim električnim sustavima

Način na koji naši električni sustavi koriste boje nisu samo za izgled.Svaka boja žice sada označava određenu funkciju, što olakšava prepoznavanje i ispravno obradu električnih komponenti tijekom u...na 1970/01/1 66937

-

Vodič za čišćenje ventila: Funkcija, simptomi, testiranje i zamjena za optimalne performanse motora

Ventil za čišćenje ključni je dio sustava automobila koji pomaže u održavanju zraka čistim upravljanjem parima goriva prije nego što mogu pobjeći u atmosferu.To ne samo da pomaže okolišu smanjenjem...na 1970/01/1 63086

-

Kvaliteta (q) Faktor: jednadžbe i aplikacije

Faktor kvalitete, ili 'q', važan je prilikom provjere koliko dobro induktori i rezonatori rade u elektroničkim sustavima koji koriste radio frekvencije (RF).'Q' mjeri koliko dobro krug minimizira g...na 1970/01/1 63025

-

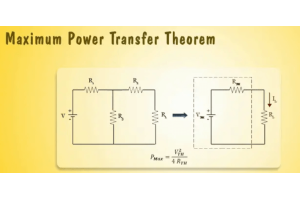

Postizanje vršnih performansi s maksimalnim teoremom prijenosa snage

Teorem maksimalnog prijenosa napajanja objašnjava kako energija iz izvora, poput baterije ili generatora, teče do povezanog opterećenja.Pokazuje točan uvjet u kojem opterećenje prima najviše snage....na 1970/01/1 54092

-

Specifikacije i kompatibilnost A23

A23 baterija je mala baterija u obliku cilindra s visokim naponom.Također se naziva 23A, 23AE ili MN21, radi na 12 volti i mnogo više od AA ili AAA baterija.Njegov poseban dizajn čini ga s...na 1970/01/1 52167