Sveobuhvatni vodič za testneče: alati i tehnike za provjeru digitalnog sustava

Ovaj vodič istražuje TestBenches, ključni alat za provjeru validacije softvera koji simulira uvjete za testiranje ulaza i provjeru izlaza.Testbenches igraju ulogu u prepoznavanju grešaka u ranom razvoju, poboljšavajući pouzdanost softvera.Uz praktične primjere i uvide, ovaj članak ističe njihovu upotrebu, tehnike i važnost u izgradnji snažnih, učinkovitih digitalnih sustava.Katalog

Uloga testnih trava u validaciji digitalnog sustava

TestBench je komponenta u procesu validacije digitalnog sustava.To nije samo alat za generiranje ulaza i provjeru izlaza, već služi kao sveobuhvatan okvir koji simulira uvjete za procjenu pouzdanosti, funkcionalnosti i ponašanja digitalnih sustava prije nego što su raspoređeni u polju.Stvaranjem kontroliranih okruženja u sustavima za testiranje stresa sa širokim rasponom ulaznih scenarija, Testbenches pomažu vam da identificirate potencijalne nedostatke dizajna u ranom životnom ciklusu razvoja, mnogo prije nego što se sustav stavi u proizvodnju.Ovo rano otkrivanje grešaka i ranjivosti potrebno je za smanjenje skupih pogrešaka, osiguravanje poštivanja specifikacija uspješnosti i poboljšanje ukupne pouzdanosti sustava.

Osim provjere ispravnosti odgovora sustava, testneke igraju ulogu u procjeni slučajeva ruba, problema s vremenom i mehanizmima za upravljanje pogreškama, osiguravajući da sustav može ispravno raditi čak i u ekstremnim ili neočekivanim uvjetima.Kroz automatizirano testiranje i simulaciju, Testbenches doprinosi većoj kvaliteti softvera, poboljšanim performansama i kraćim ciklusima razvoja omogućujući iterativno testiranje bez ručne intervencije.Oni služe kao zaštita od neuspjeha koji bi se mogli dogoditi nakon implementacije, osiguravajući robusnost i pouzdanost digitalnih sustava.

Ključne komponente testnog i njihovih funkcija

Da biste bolje razumjeli kako djeluju test, važno je istražiti komponente koje ih čine učinkovitim.Dobro izrađena testna kolica djeluje upravljajući dva osnovna zadatka: generiranje ulaza (podražaja) i provjere izlaza.Ispitajmo detaljno svaku komponentu.

Generacija podražaja

Stvaranje podražaja uključuje stvaranje skupa ulaznih signala koji simuliraju uvjete za testiranje ponašanja digitalnog sustava.Ovi unosi moraju biti i precizni i realni kako bi se osiguralo da je sustav podvrgnut različitim scenarijima s kojima bi se mogao susresti u praksi.Razmotrite osnovni RAM modul kao primjer.TestBench mora dostaviti specifične ulaze u modul i promatrati njegove rezultate kako bi se osiguralo da se ponaša kako se očekuje.Ključni ulazi za RAM modul obično uključuju:

• CLK (sat): pokreće vrijeme sustava.

• Addr (adresa): Određuje koje lokacije podataka treba pristupiti.

• WEN (Write Enable): kontrolira jesu li podaci napisani u memoriju.

• Podaci: Stvarni podaci koji se pišu u modul.

Izlaz, poznat kao Dataut, predstavlja rezultat unutarnjih operacija modula.Pažljivim skriptiranjem kako se ovi ulazi isporučuju i nadgledaju podatke, možete provjeriti da li sustav pravilno izvodi u različitim scenarijima.Razmislite o stvaranju podražaja kao postavljanju testnog scenarija u laboratoriju.Kao što znanstvenici pažljivo kontroliraju uvjete kako bi promatrali kemijske reakcije, digitalni dizajneri izrađuju precizne unose kako bi promatrali kako sustav reagira.

Izlazna provjera

Izlazna provjera je postupak provjere da li stvarni izlazi sustava odgovaraju očekivanim rezultatima.Ovaj je korak presudan za rano uhvatiti pogreške prije nego što se razviju u veća pitanja.Drugi koriste izlaznu provjeru kako bi potvrdili da sustav ispunjava svoju predviđenu funkcionalnost i dosljedno se vrši u različitim uvjetima.Izlazna provjera uključuje i automatizirane i ručne provjere.Na primjer:

• Automatizirani alati za provjeru: Alati poput ModelsIm i Quartus omogućuju automatizirano testiranje, gdje se izlazi sustava uspoređuju s očekivanim rezultatima.To ubrzava postupak provjere i smanjuje pogrešku.

• Ručna provjera (neobavezno): Za složenije scenarije možda će biti potrebne ručne provjere kako bi se osiguralo pokrivanje određenih rubnih slučajeva.

Alati i tehnike za implementaciju testnench -a

Quartus: Simulacija vizualnog ulaza/izlaza

Quartus pruža grafičko sučelje koje vizualno raspoređuje ulaze i promatra izlaze.Ova metoda može biti korisna za početnike ili za sustave koji zahtijevaju više praktični, vizualni pristup.Omogućujući interakciju sa simulacijom kroz grafičko okruženje, Quartus pomaže demistificiranju odnosa između uloga i izlaza, olakšavajući razumijevanje kako se digitalni sustav ponaša na vrijeme.Jedna od ključnih snaga Quartusa je ta što je idealna za početnike.Njegovo intuitivno, vizualno sučelje pruža izravan način da se vidi kako ulazi utječu na izlaze bez potrebe za opsežnim znanjem o skriptiranju ili programiranju.Povratne informacije koje nude pomažu lakše shvatiti ponašanje krugova, što ga čini korisnim alatom za one nove u dizajnu digitalnog sustava.Međutim, Quartus ima svoja ograničenja.Postavljanje simulacija u kvartusu može biti dugotrajno, posebno za složenije dizajne.Alat je manje fleksibilan u usporedbi s simulacijskim alatima temeljenim na skripti, koji mogu ponuditi više mogućnosti prilagodbe i automatizacije.Za rad na velikim ili vrlo detaljnim sustavima, ovaj nedostatak fleksibilnosti može predstavljati izazov.

ModelsIm: simulacija temeljena na tekstu pomoću skriptiranja

ModelsIM koristi drugačiji pristup simulaciji prioritetom unosa temeljenog na tekstu putem skriptiranja.Stvorite scenarije ispitivanja pomoću skripta Verilog (.V) ili VHDL (.VHD), a ne vizualno raspoređivanje ulaza i izlaza.Ova metoda pruža više preciznosti i kontrole.Umjesto da se oslanjate na grafičko sučelje, definirate kako sustav treba testirati kroz detaljne skripte, omogućujući veću prilagodbu i automatizaciju u postupku simulacije.Jedna od ključnih snaga ModelIM -a je fleksibilnost koju nudi.Korištenjem skripti imate više kontrole nad scenarijima ispitivanja, omogućujući im stvaranje složenih i preciznih simulacija.Jednom kada je dizajner upoznat sa sintaksom i tijekom rada, postavljanje simulacija može biti mnogo brže u usporedbi s korištenjem grafičkih alata poput Quartusa.Sposobnost ponovne upotrebe i izmjene skripti također dodaje njegovu učinkovitost, posebno u većim projektima.Međutim, tekstualni pristup ModelsIM-a dolazi s određenim ograničenjima.Zahtijeva čvrsto razumijevanje sintakse Verilog ili VHDL, što može predstavljati izazov za početnike koji nisu upoznati s jezicima opisa hardvera.Kao rezultat toga, ModelsIM ima strmiju krivulju učenja u usporedbi s više alata za vizualnu simulaciju.Novim korisnicima možda će teško započeti, ali s praksom preciznost i fleksibilnost koje nudi skriptiranje mogu postati vrijedna imovina.

Teorija premošćivanja i praksa u provjeri

Testneshes služe kao most između teorijskih dizajna i aplikacija simulirajući kako će se digitalni sustav ponašati u različitim uvjetima, uključujući rubne slučajeve i neočekivane ulaze.U digitalnom dizajnu često je teško predvidjeti kako će se sustav izvoditi u praksi temeljeno isključivo na teorijskim modelima.Testbenches zatvaraju ovaj jaz omogućujući vam da nadiđete izvan apstraktnih koncepata dizajna i procijenite ponašanje sustava u kontroliranom, simuliranom okruženju.Jedna od ključnih prednosti korištenja simulacijskih alata u TestBenchesu je trenutna povratna informacija koju pružaju tijekom uklanjanja pogrešaka.Alati poput MultiSim ili ModelsIM nude vizualne prikaze ponašanja sustava, pokazujući kako promjene u ulazu utječu na rezultate tijekom vremena.Ova povratna informacija omogućuje vam da brže odredite probleme, pogreške u praćenju praćenja u njihov temeljni uzrok i u skladu s tim prilagodite njihove nacrte.Na primjer, ako sustav ne ispuni ograničenja vremena ili pokazuje neočekivano ponašanje u određenim ulaznim sekvencama, TestBench može odmah istaknuti ove nedostatke, mnogo prije nego što je sustav fizički izgrađen.Identificirajući probleme u ranom dizajnerskom ciklusu, testni su smanjuju potrebu za skupim preradom i fizičkim prototipiranjem, pojednostavljujući postupak provjere.Ova validacija u ranoj fazi pomaže osigurati da su digitalni sustavi funkcionalno ispravni i otporni na uvjete, što ih čini pouzdanijim i smanjujući rizik od neuspjeha nakon implementacije.Na taj način, testnekes djeluje kao praktično sredstvo za pretvaranje teorijskih dizajna u robustan.

Napredna testna arhitektura

Napredni testni pregledi nadilaze jednostavno testiranje ulaznog izlaza uključivanjem dodatnih komponenti za upravljanje složenim sustavima.Standardni test sadrže tri ključna dijela: a Generator podražaja Za stvaranje ulaznih signala, a Dizajn pod testom (DUT), koji je stvarni hardver koji se testira i Izlazni monitor To provjerava izlaze u odnosu na očekivane rezultate.Ove komponente rade zajedno kako bi osigurali temeljitiju i precizniju provjeru digitalnih dizajna.

Poboljšanje točnosti testnench -a uključuje korištenje tehnika koje osiguravaju da se dizajn pouzdano izvodi u različitim scenarijima. Nasumično testiranje Uvodi nepredvidive uzorke za provjeru stabilnosti sustava u različitim uvjetima. Ispitivanje rubnih slučajeva Usredotočuje se na granične situacije u kojima sustav najvjerojatnije naiđe na pogreške.Na kraju, Regresijsko testiranje Uključuje ponovno pokretanje testova nakon promjena kako bi se potvrdilo da nisu uvedena nova pitanja, osiguravajući da sustav ostane dosljedan i bez grešaka s vremenom.

Scripting Testbenches

Da biste stvorili učinkovite i pouzdane testne naselje u Verilog ili VHDL, slijedite ključne najbolje prakse.Počnite jednostavno, a zatim proširite testiranjem osnovne funkcionalnosti prvo i postupno dodavanjem složenijih scenarija.Upotrijebite komentare i dokumentaciju kako biste lakše razumjeli i održavali svoje skripte jasno objašnjavajući svaki odjeljak.Konačno, automatizirajte gdje je to moguće kako biste uštedjeli vrijeme i smanjili pogreške pomoću petlji i funkcija za rukovanje ponavljajućim zadacima i ulaznim uzorcima.

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

Loop Digital Faze zaključana (DPLL): Dizajn, komponente i operacije

na 2025/01/7

Evolucija i utjecaj RISC arhitekture u modernom računanju

na 2025/01/7

Popularni postovi

-

Složeni računali s uputama: Kako su promijenili računanje?

na 8000/04/18 147764

-

USB-C pinout i značajke

na 2000/04/18 111987

-

Korištenje Xilinx Unified simulacijski primitivi: sveobuhvatni vodič za dizajn i simulaciju FPGA

na 1600/04/18 111351

-

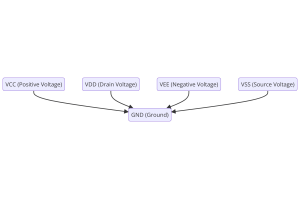

Naponi napajanja u elektronici: Značenje VCC, VDD, VEE, VSS i GND

na 0400/04/18 83751

-

RJ45 Vodič za priključak: pinout, ožičenje, vrste kabela i upotreba

na 1970/01/1 79542

-

Krajnji vodič za kodove u boji žice u modernim električnim sustavima

Način na koji naši električni sustavi koriste boje nisu samo za izgled.Svaka boja žice sada označava određenu funkciju, što olakšava prepoznavanje i ispravno obradu električnih komponenti tijekom u...na 1970/01/1 66949

-

Vodič za čišćenje ventila: Funkcija, simptomi, testiranje i zamjena za optimalne performanse motora

Ventil za čišćenje ključni je dio sustava automobila koji pomaže u održavanju zraka čistim upravljanjem parima goriva prije nego što mogu pobjeći u atmosferu.To ne samo da pomaže okolišu smanjenjem...na 1970/01/1 63089

-

Kvaliteta (q) Faktor: jednadžbe i aplikacije

Faktor kvalitete, ili 'q', važan je prilikom provjere koliko dobro induktori i rezonatori rade u elektroničkim sustavima koji koriste radio frekvencije (RF).'Q' mjeri koliko dobro krug minimizira g...na 1970/01/1 63028

-

Postizanje vršnih performansi s maksimalnim teoremom prijenosa snage

Teorem maksimalnog prijenosa napajanja objašnjava kako energija iz izvora, poput baterije ili generatora, teče do povezanog opterećenja.Pokazuje točan uvjet u kojem opterećenje prima najviše snage....na 1970/01/1 54092

-

Specifikacije i kompatibilnost A23

A23 baterija je mala baterija u obliku cilindra s visokim naponom.Također se naziva 23A, 23AE ili MN21, radi na 12 volti i mnogo više od AA ili AAA baterija.Njegov poseban dizajn čini ga s...na 1970/01/1 52172