EP1C4F400C8 FPGA: Značajke, specifikacije, programiranje i alternative

Ako radite s programibilnom logikom, EP1C4F400C8 pruža vam praktičnu ravnotežu performansi i troškova.U ovom ćete članku naučiti što je ovaj FPGA, njegove ključne značajke poput logičkog kapaciteta, memorije i I/O opcija i kako njegova struktura podržava pouzdan dizajn.Također ćete vidjeti njegove specifikacije, aplikacije u sustavima, proces programiranja i kako se uspoređuje sa sličnim dijelovima.Katalog

Što je EP1C4F400C8?

A EP1C4F400C8 član je Intelove (ranije Altera) Cyclone FPGA obitelji, zamišljeno kao isplativo i pouzdano programibilno logičko rješenje.Izgrađen na SRAM procesu od 0,13 µm, ovaj uređaj nudi umjerenu logičku gustoću i fleksibilne I/O mogućnosti unutar kompaktnog FBGA-400 paketa.Obitelj ciklona, koja uključuje uređaje poput EP1C3, EP1C6, EP1C12 i EP1C20, stvorena je kako bi uravnotežila performanse i pristupačnost za skalabilne dizajne, omogućujući jednostavnu migraciju između razine gustoće i paketa.Poznat po stabilnosti i širokom usvajanju, ostaje pouzdan izbor u naslijeđenim dizajnima.

Tražite EP1C4F400C8?Kontaktirajte nas kako biste provjerili trenutne zalihe, vrijeme i cijene.

EP1C4F400C8 CAD modeli

EP1C4F400C8 simbol

EP1C4F400C8

EP1C4F400C8 3D model

EP1C4F400C8

• Logika

EP1C4F400C8 nudi oko 4000 logičkih elemenata, organiziranih u 400 blokova logičkog niza (laboratorij).To ga čini prikladnim za dizajne srednjeg raspona koji zahtijevaju umjerenu gustoću logike uz održavanje troškovne učinkovitosti.

• Ugrađena memorija

Integrira oko 76,5 kbita ugrađene memorije.Ovaj unutarnji RAM -a podržava puferiranje podataka, pohranu i male memorijske funkcije, smanjujući potrebu za vanjskim memorijskim komponentama u mnogim dizajnima.

• Visok I/O broja

Uređaj osigurava 301 I/O igle za konfiguriranje korisnika u svom FBGA paketu od 400 lopta.Ovaj visoki broj pin omogućuje bogato povezivanje za složene sustave koji zahtijevaju više perifernih sučelja.

• Široka podrška I/O standarda

Podržava više I/O standarda, uključujući LVTTL, LVCMOS, SSTL-2, SSTL-3 i diferencijalne LVD-ove.Ova fleksibilnost omogućuje FPGA da se izravno sučelja s raznim modernim logičkim obiteljima i memorijskim uređajima.

• Diferencijalna signalizacija velike brzine

S podrškom LVDS -a do 640 Mbps, FPGA upravlja brzim zahtjevima za prijenosom podataka.To ga čini praktičnim za aplikacije kao što su brze komunikacijske veze i brza digitalna sučelja.

• Upravljanje satom s PLLS -om

CHIP integrira dvije petlje s zaključanim fazama (PLLS) i osam globalnih mreža takta.Ove značajke omogućuju preciznu generiranje, množenje i podrhtavanje kontrole za vremenski kritične primjene.

• Jezgra niskog napona

Rad na nominalnom naponu od 1,5 V, uređaj uravnotežuje performanse s manjom potrošnjom energije.Ova razina napona optimizirana je za CMOS tehnologiju od 0,13 µm koja se koristi u njegovoj izradi.

• Fleksibilni I/O naponi

FPGA podržava I/O napone od 1,5 V, 1,8 V, 2,5 V i 3,3 V u različitim bankama.Ova svestranost omogućuje mu da se sučelja s naslijeđenim i modernim komponentama sustava.

• Konfiguracija temeljena na SRAM-u

Kao i drugi ciklonski FPGA, on se temelji na SRAM-u i zahtijeva rekonfiguraciju pri svakom napajanju.To pruža fleksibilnost za ažuriranja, ali također zahtijeva vanjski konfiguracijski uređaj ili kontroler.

• Podrška za kompresiju bitstream

EP1C4F400C8 podržava učitavanje komprimiranog bita tijekom konfiguracije.To smanjuje zahtjeve vanjske memorije i ubrzava vrijeme konfiguracije.

• PCI usklađenost

Uključuje ugrađenu podršku za PCI standarde (33/66 MHz, 32/64-bitni).Ova značajka omogućuje da se uređaj izravno integrira u sustave koji zahtijevaju PCI povezivanje bez dodatne logike premošćivanja.

Struktura ciklonskog laboratorija

Dijagram prikazuje strukturu bloka logičkog niza (laboratorij) koja se koristi u ciklonskim FPGA -ima poput EP1C4F400C8.Svaki se laboratorij povezuje s mrežom međusobnih povezanosti: međusobno povezivanje redaka, međusobno povezivanje stupaca i lokalni međusobno povezivanje, koji usmjeravaju signale između logičkih elemenata i drugih blokova.Izravna veza međusobno povezivanje pružaju brze, niske staze do susjednih laboratorija, poboljšavajući vremenske performanse u signalnim putovima.Ova je arhitektura važna jer uravnotežuje fleksibilnost usmjeravanja s učinkovitošću, omogućavajući FPGA da upravlja složenim dizajnom, a istovremeno drži brzinu i optimizirano područje.

Dijagram ciklona I/O banke

Dijagram ilustrira I/O banku strukturu ciklona FPGA kao što je EP1C4F400C8.Uređaj je podijeljen u četiri I/O banke, od kojih se svaki napaja vlastitim sabirnicama, omogućavajući miješanje različitih naponskih standarda unutar jednog FPGA.Sve banke podržavaju širok raspon I/O standarda, uključujući LVTTL, LVCMOS, LVDS, RSD i SSTL, dok banke 1 i 3 također podržavaju 3.3-V PCI za kompatibilnost s naslijeđenim sustavima.Ova fleksibilna I/O arhitektura važna je jer omogućava bešavnu integraciju s različitim vanjskim uređajima i sučeljima, čineći FPGA prilagodljivu različitim aplikacijama.

EP1C4F400C8 Specifikacije

|

Tip |

Parametar |

|

Proizvođač |

Altera/Intel |

|

Niz |

Ciklon® |

|

Pakiranje |

Pladanj |

|

Status dijela |

Zastario |

|

Broj laboratorija/CLB -a |

400 |

|

Broj logičkih elemenata/stanica |

4000 |

|

Ukupni RAM komadići |

78.336 |

|

Broj I/O |

301 |

|

Napon - napad |

1.425V ~ 1.575V |

|

Montažni tip |

Površinski nosač |

|

Radna temperatura |

0 ° C ~ 85 ° C (TJ) |

|

Paket / slučaj |

400-bGa |

|

Paket uređaja dobavljača |

400-FBGA (21 × 21) |

|

Broj osnovnog proizvoda |

EP1C4 |

EP1C4F400C8 Aplikacije

1. Digitalna obrada signala (DSP)

EP1C4F400C8 može se programirati za obavljanje zadataka kao što su filtriranje, FFT i signalna modulacija.Njegova kombinacija logičkih elemenata i ugrađene memorije čini ga prikladnim za obradu velike brzine.To mu omogućava da zamijeni tradicionalne DSP čipove fleksibilnim FPGA rješenjem koje se može reprogramirati za različite algoritme.

2. Ugrađeni i upravljački sustavi

U industrijskim i ugrađenim sustavima, ovaj se FPGA često koristi za implementaciju prilagođenih kontrolera, sekvence i državnih strojeva.Njegova rekonfigurabilna logika omogućuje prilagođavanje hardverskog ponašanja precizno potrebama sustava.Integriranjem kontrolne logike unutar FPGA smanjuje se broj vanjskih komponenti, poboljšavajući pouzdanost i snižavanje troškova.

3. Premošćivanje komunikacije i sučelja

Uređaj podržava više I/O standarda i može djelovati kao most između različitih komunikacijskih protokola.Često se koristi za povezivanje PCI, LVD -a, SDRAM -a i ostalih sučelja neometano unutar sustava.To ga čini vrlo korisnim u mrežnoj opremi, ugrađenim kontrolerima i pretvorbi sučelja s nasljeđenim do modernim sučeljem.

4. Prikupljanje podataka i obrada

S velikom I/O dostupnošću i fleksibilnom memorijom, EP1C4F400C8 dobro je prilagođen za sustave prikupljanja podataka.Može se izravno sučeljavati s ADC -ovima i senzorima, obraditi podatke na vrijeme i pripremiti ih za pohranu ili prijenos.Takve su primjene uobičajene u medicinskim instrumentima, ispitnoj opremi i znanstvenim mjernim uređajima.

Ep1c4f400c8 slični dijelovi

|

Specifikacija |

EP1C4F400C8 |

EP1C4F400C8N |

Ep1c4f400c8naa |

EP1C4F400C6N |

Ep1c4f324c8n |

Ep1c4t144c8n |

|

Proizvođač |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

Obitelj fpga |

Ciklona (EP1C4) |

Ciklona (EP1C4) |

Ciklona (EP1C4) |

Ciklona (EP1C4) |

Ciklona (EP1C4) |

Ciklona (EP1C4) |

|

Logički elementi (LES) |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

|

Ugrađena memorija (bitovi) |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

|

I/O igle |

301 |

301 |

301 |

301 |

249 |

97 |

|

Paket / slučaj |

400-fbga |

400-fbga |

400-fbga |

400-fbga |

324-FBGA |

144-TQFP |

|

Brzina brzina |

C8 |

C8 |

C8 |

C6 (brže) |

C8 |

C8 |

|

Temeljni napon |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

|

Operativna temp.Raspon |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C

|

EP1C4F400C8 Koraci programiranja

Prije nego što možete koristiti EP1C4F400C8 FPGA, svoj dizajn morate učitati u uređaj.Programiranje uključuje konfiguriranje FPGA s datotekom bitstream -a, tako da se zna kako se ponašati kao predviđeni krug.

1. Odaberite shemu konfiguracije i postavite MSEL PINS

Započinjete odabirom konfiguracijske sheme koja najbolje odgovara vašem postavljanju, poput aktivnog serijskog, pasivnog serijskog ili JTAG -a.To se postiže postavljanjem MSEL pinova na određene razine logike prije napajanja.Svaki način koristi različite igle i protokole, tako da morate potvrditi kompatibilnost sa svojim dizajnerskim alatima i konfiguracijskom memorijom.Donošenje pravog izbora ovdje osigurava postupak glatke konfiguracije.

2. Primijenite napajanje i inicijalizirajte uređaj

Zatim uključite jezgru FPGA i I/O šine unutar navedenih raspona napona.Tijekom pokretanja, držite Nonfig pin nizak da biste držali uređaj u resetiranju dok naponi napajanja nisu stabilni.Jednom stabilno, oslobađate resetiranje i uređaj signalizira spremnost vožnjom Nstatus pin.To jamči da se FPGA pravilno inicijalizira prije nego što započne konfiguracija.

3.

U ovoj fazi šaljete datoteku podataka konfiguracije (bitstream) u FPGA pomoću odabrane sheme.U aktivnom serijskom ili pasivnom serijskom načinu, bitstream dolazi iz uređaja vanjske memorije, dok JTAG omogućuje izravno programiranje putem kabela.Uređaj se neprestano čita u podacima o konfiguraciji dok se ne završi.Vaš dizajnerski softver generira ovaj bitstream kako bi odgovarao vašim logičkim zahtjevima.

4. Potvrdite uspješnu konfiguraciju (conf_done)

Kad FPGA završi učitavanje, on tvrdi da je CONF_DONE pin kako bi pokazao da su podaci o konfiguraciji uspješno primljeni.Istodobno, uređaj izvodi internu inicijalizaciju poput čišćenja registara i aktiviranja I/O.Ako conf_done ne uspije visoko, to obično znači da podaci o konfiguraciji ili postavku imaju pogrešku.Gledanje ovog pin -a najjednostavniji je način provjere da li je postupak dovršen.

5. Izvršite neobavezno konfiguraciju u sustavu

Na kraju, imate mogućnost ažuriranja ili reprogramiranja FPGA bez uklanjanja s ploče.Koristeći JTAG ili ugrađeni kontroler, možete izravno učitati novi BitStream, što je korisno za ažuriranja firmvera.Ova fleksibilnost omogućuje vam izmjenu, uklanjanje pogrešaka ili nadogradnju vašeg sustava čak i nakon implementacije.Osigurava da se vaš dizajn temeljen na FPGA može s vremenom prilagoditi promjenjivim zahtjevima.

EP1C4F400C8 Prednosti i nedostaci

Prednosti

• ekonomičan izbor za dizajne srednjeg raspona

• Visoki I/O Broj u usporedbi sa uređajima slične gustoće

• Fleksibilan napon i I/O standardni potpora

• Podržana zrelim alatima i dokumentacijom

• Niža upotreba energije od starijih generacija FPGA

Nedostaci

• zastarjeli ograničenom dugoročnom dostupnošću

• Niži kapacitet logike i memorije u odnosu na moderne FPGAS

• Sporije radne brzine i I/O performanse

• zahtijeva vanjsku memoriju za konfiguraciju na napajanju

• Nedostaju napredne značajke poput DSP blokova i brzih primopredajnika

EP1C4F400C8 Dimenzije pakiranja

|

Tip |

Parametar |

|

Vrsta paketa |

FBGA (fini niz kuglica) |

|

Brojanje lopte |

400 |

|

Kuglica (e) |

1,0 mm (tipično za ciklon EP1C4F400) |

|

Promjer kuglice (b) |

0,45 mm (nominalno) |

|

Veličina paketa (d × e) |

21 mm × 21 mm |

|

Visina paketa (a) |

2,40 mm (max) |

|

Debljina supstrata (A2) |

~ 0,40 mm |

|

Debljina poklopca kalupa (A3) |

~ 1,90 mm |

|

Visina lopte (A1) |

0,25 mm (nominalno) |

|

PIN A1 kutak |

Označeno za orijentaciju |

|

Izgled nizova |

20 × 20 rešetka (s kuglicama koje nedostaju) |

|

Montaža |

Površinski nosač (SMD) |

EP1C4F400C8 Proizvođač

EP1C4F400C8 je izvorno proizveo Korporacija alware, pionir u programabilnim logičkim uređajima i FPGA tehnologiji.U 2015. godini Altera je stekao Intel Corporation, a linija proizvoda postala je dio Intelove Group programabilnih rješenja (PSG).Danas Intel podržava ove naslijeđene Altera uređaje, usredotočujući se na razvoj na novijih FPGA obitelji, osiguravajući kontinuitet za postojeće korisnike i unapređivanje inovacija u programabilnoj logici.

Zaključak

EP1C4F400C8 ističe se kao ekonomičan i svestran FPGA koji nudi solidne performanse za dizajn srednjeg raspona.Sa svojih 4000 logičkih elemenata, ugrađene memorije, opsežnim I/O podrškom i kompatibilnošću s višestrukim standardima napona i sučelja, on pruža fleksibilnost u različitim aplikacijama.Njegova arhitektura, proces programiranja i široka upotrebljivost u DSP -u, ugrađeni sustavi i prikupljanje podataka čine ga praktičnim izborom unatoč svom naslijeđenom statusu.Iako nedostaju napredne značajke koje se nalaze u novijim uređajima i suočava se s ograničenom dugoročnom dostupnošću, ostaje pouzdana opcija koja traži dokazana rješenja u skalabilnim FPGA dizajnima.

Podatkovni list pdf

EP1C4F400C8 podatkovne liste:

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

Često postavljana pitanja [FAQ]

1. Koji su alati potrebni za programiranje EP1C4F400C8?

Potreban vam je Intelov softver Quartus (prethodno Altera Quartus II) zajedno s podržanim programskim kabelom poput USB-Blaster.Ovi alati omogućuju vam stvaranje bitstream -a i učitavanje u FPGA.

2. Može li EP1C4F400C8 izravno obraditi PCI aplikacije?

Da, ima ugrađenu usklađenost za PCI standarde (33/66 MHz, 32/64-bitni), što ga čini prikladnim za integraciju sustava temeljenog na PCI bez potrebe za dodatnom logikom premošćivanja.

3. Što se događa ako EP1C4F400C8 ne uspije tijekom konfiguracije?

Ako konfiguracija ne uspije, pin conf_done neće tvrditi visok.To obično ukazuje na pogrešku u datoteci BitStream, sekvenciranju napona ili postavljanju PIN -a, a treba ih ponovno provjeriti u vašem protoku dizajna.

4. Može li EP1C4F400C8 sučelje izravno s DDR memorijom?

Podržava nekoliko I/O standarda, ali nema izvorna DDR sučelja poput modernih FPGA -ova.Možda će biti potrebna dodatna razmatranja dizajna ili premošćivanje komponenti.

5. Kako se EP1C4F400C8 uspoređuje s novijim FPGAS -om?

U usporedbi s modernim uređajima, EP1C4F400C8 ima manju brzinu, manju logičku gustoću i manje naprednih značajki.Međutim, ostaje ekonomičan izbor za stabilne dizajne srednjeg opsega u kojima nisu potrebni vrhunski performanse.

EPM3256AFC256-7 CPLD pregled: Značajke, pinout, programiranje i aplikacije

na 2025/10/3

ADG432BR Analogni prekidač IC: Specifikacije, pinout, alternative i podatkovni list

na 2025/10/2

Popularni postovi

-

Složeni računali s uputama: Kako su promijenili računanje?

na 8000/04/18 147778

-

USB-C pinout i značajke

na 2000/04/18 112029

-

Korištenje Xilinx Unified simulacijski primitivi: sveobuhvatni vodič za dizajn i simulaciju FPGA

na 1600/04/18 111351

-

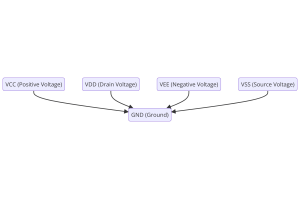

Naponi napajanja u elektronici: Značenje VCC, VDD, VEE, VSS i GND

na 0400/04/18 83782

-

RJ45 Vodič za priključak: pinout, ožičenje, vrste kabela i upotreba

na 1970/01/1 79579

-

Krajnji vodič za kodove u boji žice u modernim električnim sustavima

Način na koji naši električni sustavi koriste boje nisu samo za izgled.Svaka boja žice sada označava određenu funkciju, što olakšava prepoznavanje i ispravno obradu električnih komponenti tijekom u...na 1970/01/1 66972

-

Vodič za čišćenje ventila: Funkcija, simptomi, testiranje i zamjena za optimalne performanse motora

Ventil za čišćenje ključni je dio sustava automobila koji pomaže u održavanju zraka čistim upravljanjem parima goriva prije nego što mogu pobjeći u atmosferu.To ne samo da pomaže okolišu smanjenjem...na 1970/01/1 63107

-

Kvaliteta (q) Faktor: jednadžbe i aplikacije

Faktor kvalitete, ili 'q', važan je prilikom provjere koliko dobro induktori i rezonatori rade u elektroničkim sustavima koji koriste radio frekvencije (RF).'Q' mjeri koliko dobro krug minimizira g...na 1970/01/1 63041

-

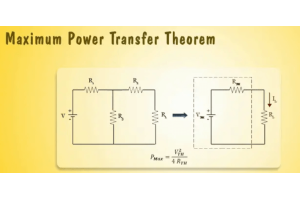

Postizanje vršnih performansi s maksimalnim teoremom prijenosa snage

Teorem maksimalnog prijenosa napajanja objašnjava kako energija iz izvora, poput baterije ili generatora, teče do povezanog opterećenja.Pokazuje točan uvjet u kojem opterećenje prima najviše snage....na 1970/01/1 54097

-

Specifikacije i kompatibilnost A23

A23 baterija je mala baterija u obliku cilindra s visokim naponom.Također se naziva 23A, 23AE ili MN21, radi na 12 volti i mnogo više od AA ili AAA baterija.Njegov poseban dizajn čini ga s...na 1970/01/1 52193