EP20K100EFC324-1X FPGA: Značajke, specifikacije, aplikacije i vodič za programiranje

EP20K100KEFC324-1X je programabilni čip (FPGA) iz Intelove serije APEX-20KE® APEX-20KE.Dizajniran je za obradu složenih digitalnih krugova i podržava obradu podataka velike brzine.Ovaj vodič objašnjava svoje značajke, specifikacije, kako ga programirati i njegove prednosti, što ga čini korisnim resursom za sve.Katalog

EP20K100EFC324-1X pregled

A EP20K100EFC324-1X dio je Intelove serije Altera Apex-20Ke®, terenskog programiranog niza vrata (FPGA) prilagođen za programirljive logičke aplikacije visoke gustoće koje zahtijevaju sofisticirane integracije sustava na programu-a-programiranje (SOPC).Ovaj se uređaj odlikuje njegovom integracijom od 4,160 logičkih elemenata ili ćelija i 416 blokova logičkog niza (laboratorija), što olakšava značajnu konfigurabilnost za različite dizajne digitalnih krugova.Također se može pohvaliti značajnom količinom ugrađene memorije koja odgovara zahtjevnim zahtjevima za pohranu podataka unutar FPGA.Daljnje poboljšanje svoje svestrane primjene, EP20K100KEFC324-1X podržava 246 I/O igle i nudi značajan broj vrata od približno 263 000 ekvivalentnih vrata, djelujući učinkovito između 1,71 V i 1,89V.Pakiran je u 324 loptu loptu za kuglu (FBGA), koji pomaže u robusnoj fizičkoj integraciji u elektroničke sklopove.

EP20K100EFC324-1X savršen je izbor kada ste spremni naručiti skupne narudžbe s nama za vaše projekte ili linije proizvoda.

EP20K100EFC324-1X CAD modeli

EP20K100EFC324-1X simbol

EP20K100EFC324-1X

EP20K100EFC324-1X 3D model

EP20K100EFC324-1X značajke

• Visoka gustoća logike: FPGA je opremljen s 4.160 logičkih elemenata (LES) i 416 blokova logičkog niza (laboratorij).Ova visoka gustoća logičkih ćelija omogućava dizajn i izvršavanje složenih digitalnih krugova i sustava unutar jednog čipa, što ga čini idealnim za aplikacije koje zahtijevaju robusne mogućnosti logičke obrade.

• Ugrađena memorija: Nudeći 53.248 RAM bita, ovaj FPGA pruža značajne ugrađene resurse memorije.Ova je značajka dobra za aplikacije koje zahtijevaju brzo pohranjivanje i pretraživanje podataka, što omogućava učinkovito rukovanje zadacima intenzivnim podacima.

• Opsežne I/O mogućnosti: S 246 ulaznih/izlaznih igle, EP20K100EFC324-1X osigurava sveobuhvatne mogućnosti povezivanja i povezivanja.Ovaj široki raspon I/O mogućnosti omogućava mu da se lako poveže s mnoštvom vanjskih uređaja i sustava, poboljšavajući njegovu korisnost u složenim elektroničkim sklopovima.

• Višenaponski potpora: Uređaj podržava raspon napona jezgre od 1,71V do 1,89V i sadrži interna multivolt ™ I/O.To omogućava da FPGA bude kompatibilna s drugim elektroničkim komponentama koje djeluju na različitim razinama logike, uključujući 1,8 V, 2,5 V, 3,3 V i 5,0V, pružajući veliku fleksibilnost u dizajnu sustava.

EP20K100EFC324-1X blok dijagram

A EP20K100EFC324-1X blok dijagram Predstavlja unutarnju strukturu uređaja FPGA (terenska programabilna vrata), koji prikazuje njegove različite funkcionalne jedinice.Dijagram se sastoji od međusobno povezanih logičkih blokova, memorijskih elemenata, upravljanja satom i I/O elemenata.U srži dizajna jesu Blokovi logičkog niza (Laboratoriji), koji sadrže Potraživanje stolova (LUTS) i logika utemeljena na proizvodu.Ovi elementi omogućuju fleksibilnu logičku implementaciju, čineći FPGA prikladnom za brzu kontrolnu logiku, državne strojeve i DSP funkcije.A FastTrack Interconect Pruža brzi komunikacijski put između logičkih elemenata, osiguravajući učinkovito usmjeravanje signala na cijelom uređaju.A Krug za upravljanje satom , uključujući značajku Clocklock -a, osigurava pouzdan i sinkronizirani rad stabilizacijom i distribucijom signala sata preko FPGA.A Ulazni/izlazni elementi (IOES), smješteni oko tkanine FPGA, služe kao sučelja za vanjsku komunikaciju.Ovi IOE podržavaju višestruke industrijske standardne protokole poput PCI,, GTL+,, SSTL-3, i LVDS, omogućujući FPGA da se sučelja s različitim vanjskim sustavima.Ovi IOE osiguravaju kompatibilnost s različitim razinama napona i signalnim standardima, povećavajući svestranost FPGA u ugrađenim aplikacijama. Ugrađeni memorijski blokovi Omogućite fleksibilna rješenja za pohranu unutar FPGA.Ti memorijski elementi mogu funkcionirati kao Memorija koja se može adresirati na adresu sadržaja (Cam), Memorija nasumičnog pristupa (OVAN), Memorija samo za čitanje (Rom), Prvi put (FIFO) međuspremnici i druge memorijske strukture.Sposobnost integriranja memorije izravno u FPGA tkaninu poboljšava učinkovitost obrade podataka, smanjujući ovisnosti o vanjskoj memoriji i kašnjenja.

EP20K100EFC324-1X Specifikacije

|

Tip |

Parametar |

|

Proizvođač |

Inteliran |

|

Niz |

Apex-20ke® |

|

Pakiranje |

Pladanj |

|

Status dijela |

Zastario |

|

Broj laboratorija/CLB -a |

416 |

|

Broj logičkih elemenata/stanica |

4160 |

|

Ukupni RAM komadići |

53248 |

|

Broj I/O |

246 |

|

Broj vrata |

263000 |

|

Napon - napad |

1,71V ~ 1,89V |

|

Montažni tip |

Površinski nosač |

|

Radna temperatura |

0 ° C ~ 85 ° C (TJ) |

|

Paket / slučaj |

324-bGa |

|

Paket uređaja dobavljača |

324-FBGA (19x19) |

|

Broj osnovnog proizvoda |

EP20K100 |

EP20K100EFC324-1X aplikacije

Umrežavanje i komunikacije

Ovaj FPGA idealan je za umrežavanje opreme kao što su usmjerivači i prekidači, gdje upravlja usmjeravanjem podataka, obradom signala i rukovanjem protokolom.Njegova visoka gustoća logike i opsežne I/O mogućnosti omogućuju mu podržavanje složenih, brzih podataka o brzini potrebnih u modernoj komunikacijskoj infrastrukturi.

Industrijski upravljački sustavi

U industrijskom sektoru, EP20K100EFC324-1X izvrsno se snalazi u automatizacijskim sustavima.Njegove programabilnosti i robusne mogućnosti obrade omogućuju preciznu kontrolu i nadzor za povećanje operativne učinkovitosti i pouzdanosti u proizvodnim procesima.

Automobilska elektronika

FPGA služi kao komponenta u automobilskim aplikacijama, posebno u naprednim sustavima za pomoć u vozaču (ADAS) i sustavima za zabavu u vozilu.Omogućuje potrebnu moć obrade i prilagodljivost za obradu podataka i podržavanje sofisticiranih funkcionalnosti potrebnih u modernim vozilima.

Potrošačka elektronika

Zbog svoje fleksibilnosti i visokih performansi, EP20K100EFC324-1X nalazi se i u potrošačkoj elektronici poput televizora visoke razlučivosti i igraćih konzola.Podržava složene funkcionalnosti i AIDS u skraćivanju ciklusa razvoja proizvoda, udovoljavajući brzoj potražnji tržišta potrošačke elektronike.

Medicinski uređaji

U medicinskom polju, ovaj FPGA doprinosi funkcionalnosti opreme za medicinsku sliku i dijagnostičkih alata.Njegova sposobnost obrade podataka velikim brzinama osigurava da ti uređaji mogu dati točne i pravovremene dijagnostičke rezultate za učinkovito liječenje i snimanje.

Ep20k100efc324-1x slični dijelovi

EP20K100EFC324-1X KORAKA

Da bi se učinkovito programirao EP20K100EFC324-1X, član serije FPGA APEX-20KE® APEX-20KE®, važno je slijediti strukturirani slijed koraka.Ovaj postupak osigurava da se vaš dizajn učinkovito prevodi u format koji FPGA može izvršiti.U nastavku opisujem detaljan pristup programiranju ovog FPGA modela, integrirajući korake i modifikacije specifične za ovaj uređaj.

1. Unos dizajna

Započnite stvaranjem dizajna digitalne logike.Koristite jezike opisa hardvera (HDL) kao što su VHDL ili Verilog, koji vam omogućuju opisivanje funkcionalnosti hardvera i logike vašeg sustava.Alati poput Altera's Quartus II nude sveobuhvatno okruženje za pisanje, testiranje i sastavljanje vašeg HDL koda.Osigurajte da je vaš dizajn modularan, što olakšava uklanjanje pogrešaka i razmjera.

2. Sinteza

Jednom kada je unos dizajna dovršen, sljedeći korak je sinteza, gdje se HDL kôd prevodi u netlistu.Ovaj netlist predstavlja međusobno povezani popis vrata, flip-flops i drugih hardverskih elemenata koji čine vaš dizajn.Tijekom sinteze, kôd je optimiziran za specifičnu arhitekturu EP20K100EFC324-1X, osiguravajući da dizajn učinkovito koristi resurse FPGA.U tu svrhu mogu se koristiti alati poput Synplify Pro ili alata za sintezu unutar kvartusa II.Važno je usredotočiti se na optimizaciju vašeg dizajna kako bi se ispunilo ograničenja vremena i resursa.

3. Provedba

Slijedeći sintezu, odvija se provedba.Ovaj korak uključuje mapiranje netliste na stvarni FPGA hardver.Uključuje postavljanje logičkih elemenata unutar FPGA i usmjeravanje veza između njih.Softver Quartus II olakšava ovaj postupak putem svojih alata za implementaciju, koji upravljaju smještajem i usmjeravanjem kako bi zadovoljili željene brzine sata i mjerne podatke o performansama.Tijekom provedbe, možda ćete trebati ponoviti svoj dizajn na temelju povratnih informacija od alata za analizu vremena kako biste osigurali ispunjeni svi zahtjevi za izvedbu.

4. Generacija bitstreama

Nakon uspješne provedbe, sljedeća faza je generiranje bitstreama.Ovo je binarna datoteka koja će se učitati na FPGA.Bitstream sadrži konfigurirane podatke za svaki programabilni element u FPGA, postavljajući uređaj za obavljanje funkcija prema vašem dizajnu.Softver Quartus II može generirati ovaj bitstream, koji je tada spreman za preuzimanje na FPGA.

5. Programiranje FPGA

Posljednji korak je programiranje FPGA s generiranim bitstreamom.To se može učiniti pomoću hardverskog programera kompatibilnog s EP20K100EFC324-1X, kao što je USB Blaster.Povežite programera na svoju razvojnu ploču gdje je FPGA montiran i koristite alat Quartus II programera za prijenos bitstream na FPGA.Ovaj će korak učitati vaš dizajn na FPGA i počet će raditi prema logici definiranoj u vašem HDL kodu.

EP20K100EFC324-1X Prednosti

Visoka integracija

EP20K100EFC324-1X nudi visoke mogućnosti integracije zbog svog velikog broja logičkih elemenata i ugrađene memorije.Ova integracija omogućuje konsolidaciju više funkcionalnosti u jedan uređaj.Kao rezultat toga, sustavi se mogu pojednostaviti, smanjujući ukupni broj komponenti, potreban fizički prostor i potencijalne točke kvara u elektroničkim dizajnima.

Fleksibilna logička implementacija

Arhitektura EP20K100EFC324-1X podržava i tablicu pretraživanja (LUT) i logiku koja se temelji na proizvodu.Ova fleksibilnost u logičkoj implementaciji omogućuje optimizaciju FPGA za širok raspon aplikacija, od jednostavnih logičkih vrata do složenih kombinacijskih krugova.Pruža prednost u smislu svestranosti dizajna i može primiti širok spektar digitalnih funkcionalnosti.

Napredna struktura međusobnog povezivanja

S hijerarhijskom strukturom međusobnog povezivanja, FPGA uključuje lokalne, Megalab ™ i FastTrack® interkonekcije.Ovi specijalizirani resursi usmjeravanja poboljšavaju učinkovitost usmjeravanja signala i poboljšavaju ukupne performanse uređaja.Ova napredna struktura međusobnog povezivanja dobra je za dizajne koji zahtijevaju prijenos podataka velike brzine i male latencije, što FPGA čini idealnim za računanje i telekomunikacije visokih performansi.

Upravljanje satom

EP20K100EFC324-1X uključuje tehnologiju Clocklock i Clockboost, koja pomaže u učinkovitom upravljanju satom.Ove značajke pomažu u održavanju integriteta signala sata tijekom FPGA, smanjenju podrhtavanja i poboljšanju pouzdanosti signala.Učinkovito upravljanje taktom potrebno je za sinkrone digitalne krugove, osiguravajući stabilan i predvidljivi rad u različitim uvjetima okoliša.

Fleksibilnost dizajna

Programirajuća priroda EP20K100EFC324-1X omogućava prilagođavanje hardvera specifičnim potrebama i ponovno konfiguriranje FPGA za različite aplikacije ili ažuriranja.Ova fleksibilnost znači da se jedan FPGA može koristiti u više projekata, što je korisno u dinamičnom tehnološkom krajoliku gdje se zahtjevi mogu brzo promijeniti.

Brzo prototipiranje

FPGA-i poput EP20K100EFC324-1X omogućuju brzo prototipiranje digitalnih krugova.Možete brzo razviti i ponavljati dizajne bez dugih vremena olova povezanih s prilagođenim ASIC razvojem.Ova sposobnost brzog modeliranja i testiranja novih dizajna ubrzava razvojni proces, što dovodi do brže inovacije i skraćenog vremena na tržište.

Troškovna učinkovitost

Integriranje više funkcija unutar jednog FPGA smanjuje potrebu za dodatnim diskretnim komponentama, što može dovesti do uštede troškova i u nabavi i u montaži.Ova integracija također pojednostavljuje proces proizvodnje i može smanjiti ukupnu složenost sustava, što dovodi do nižih troškova održavanja i nadogradnje tijekom životnog ciklusa proizvoda.

Dugoročna podrška

Rekonfigurabilni aspekt EP20K100EFC324-1X osigurava da se hardver može ažurirati kako bi se popravili pogreške, poboljšali performanse ili dodali nove značajke bez potrebe za fizičkim promjenama hardvera.Ova dugoročna podrška i prilagodljivost štite ulaganja i omogućuju uređajima da ostanu relevantni kako se pojavljuju novi standardi i tehnologije.

EP20K100EFC324-1X Dimenzije pakiranja

EP20K100EFC324-1X je FPGA iz serije APEX-20KE® APEX-20KE®, smještena u a 324 lopta lopta rešetka (FBGA) paket.Njegove dimenzije pakiranja su sljedeće:

• Nagib: 1 mm

• Duljina × širina: 19 mm × 19 mm

• Područje: 361 mm²

EP20K100EFC324-1X Proizvođač

EP20K100KEFC324-1X model je iz serije Apex-20KE® poljskih programabilnih nizova vrata (FPGAS) koje je izvorno razvila ALTERA.Nakon Intelove akvizicije Altera 2015. godine, ovaj FPGA i drugi proizvodi Allera postali su dio Intelovog opsežnog portfelja programibilnih rješenja.Kao rezultat, Inteliran Nastavlja podržavati linije proizvoda Altera, istovremeno ih integrirajući s vlastitom ponudom napredne tehnologije.Iako je EP20K100KEFC324-1X klasificiran kao zastarjeli i više nije u proizvodnji, njegovo naslijeđe održava se u Intelu, što preporučuje novije modele FPGA za trenutne aplikacije kako bi se osigurala dugoročna podrška i dostupnost.

Zaključak

EP20K100EFC324-1X moćan je i fleksibilan FPGA koji omogućava stvaranje i testiranje prilagođenih digitalnih krugova.Nudi visoke performanse, ugrađenu memoriju i višenaponsku podršku, što ga čini korisnim u mnogim industrijama.Ovaj vodič proveo vas je kroz glavne značajke, dizajn i korake za programiranje ovog FPGA na jednostavan način, tako da ga lako možete razumjeti i koristiti.

Podatkovni list pdf

EP20K100EFC324-1X podataka:

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

Često postavljana pitanja [FAQ]

1. Kako se EP20K100EFC324-1X uspoređuje s novijim FPGA modelima?

EP20K100EFC324-1X ostaje moćan FPGA za naslijeđene sustave i industrijske primjene koje zahtijevaju visoku gustoću logike i fleksibilne I/O mogućnosti.Međutim, u usporedbi s modernim FPGAS-om poput Intelove serije Cyclone, Arria ili Stratix, nedostaje mu napredna učinkovitost energije, brzi primopredajnik i ubrzanje vođen AI.Ako dizajnirate novi sustav, možemo predložiti ekvivalentne ili nadograđene modele.

2. Podržava li EP20K100EFC324-1X vanjska memorijska sučelja poput DDR-a ili SRAM-a?

Da, EP20K100EFC324-1X podržava vanjska memorijska sučelja, uključujući SRAM i SDRAM.Međutim, on ne podržava DDR2/DDR3.Ako je potrebno vezos memorije velike brzine, možda će biti potrebna dodatna vanjska logika ili novija FPGA.

3. Mogu li ponovno konfigurirati EP20K100EFC324-1X više puta?

Da, kao i svi FPGAS, ovaj je uređaj potpuno reprogramiran.Međutim, ako koristite isparnu konfiguraciju, trebat će vam vanjska memorija (poput serijskog maturanta) za zadržavanje dizajna nakon biciklizma u napajanju.

4. Mogu li programirati EP20K100EFC324-1X pomoću Intel Quartus softvera?

Da, možete programirati EP20K100EFC324-1X pomoću Intel Quartus II (naslijeđene verzije), jer ovaj FPGA pripada obitelji Apex-20KE®.Osigurajte da vaša verzija Quartus II podržava ovaj uređaj, jer novija izdanja Quartus Prime ne podržavaju naslijeđene FPGAS.

5. Koje zahtjeve za napajanje trebam uzeti u obzir prilikom korištenja EP20K100EFC324-1X?

EP20K100EFC324-1X djeluje s rasponom napona jezgre od 1,71V do 1,89V.Također sadrži multivolt ™ I/O tehnologiju, podržavajući 1,8V, 2,5V, 3,3V i 5,0V razinu logike.Osigurajte da vaše napajanje ispunjava ove zahtjeve za naponom za stabilne performanse.

XCV200-6FG456C FPGA: Značajke, specifikacije, programiranje i aplikacije

na 2025/03/20

Zašto su komponente 0603 popularne u modernoj elektronici

na 2025/03/20

Popularni postovi

-

Složeni računali s uputama: Kako su promijenili računanje?

na 8000/04/18 147770

-

USB-C pinout i značajke

na 2000/04/18 112006

-

Korištenje Xilinx Unified simulacijski primitivi: sveobuhvatni vodič za dizajn i simulaciju FPGA

na 1600/04/18 111351

-

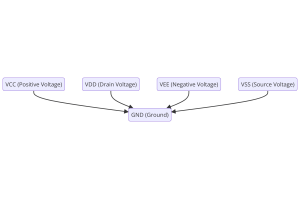

Naponi napajanja u elektronici: Značenje VCC, VDD, VEE, VSS i GND

na 0400/04/18 83768

-

RJ45 Vodič za priključak: pinout, ožičenje, vrste kabela i upotreba

na 1970/01/1 79562

-

Krajnji vodič za kodove u boji žice u modernim električnim sustavima

Način na koji naši električni sustavi koriste boje nisu samo za izgled.Svaka boja žice sada označava određenu funkciju, što olakšava prepoznavanje i ispravno obradu električnih komponenti tijekom u...na 1970/01/1 66959

-

Vodič za čišćenje ventila: Funkcija, simptomi, testiranje i zamjena za optimalne performanse motora

Ventil za čišćenje ključni je dio sustava automobila koji pomaže u održavanju zraka čistim upravljanjem parima goriva prije nego što mogu pobjeći u atmosferu.To ne samo da pomaže okolišu smanjenjem...na 1970/01/1 63098

-

Kvaliteta (q) Faktor: jednadžbe i aplikacije

Faktor kvalitete, ili 'q', važan je prilikom provjere koliko dobro induktori i rezonatori rade u elektroničkim sustavima koji koriste radio frekvencije (RF).'Q' mjeri koliko dobro krug minimizira g...na 1970/01/1 63040

-

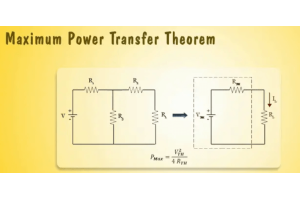

Postizanje vršnih performansi s maksimalnim teoremom prijenosa snage

Teorem maksimalnog prijenosa napajanja objašnjava kako energija iz izvora, poput baterije ili generatora, teče do povezanog opterećenja.Pokazuje točan uvjet u kojem opterećenje prima najviše snage....na 1970/01/1 54095

-

Specifikacije i kompatibilnost A23

A23 baterija je mala baterija u obliku cilindra s visokim naponom.Također se naziva 23A, 23AE ili MN21, radi na 12 volti i mnogo više od AA ili AAA baterija.Njegov poseban dizajn čini ga s...na 1970/01/1 52184