EP2S60F672C4 FPGA: Značajke, aplikacije, programiranje i vodič podataka

U ovom ćete vodiču dobiti jasan pregled EP2S60F672C4, moćnog FPGA iz Intelove obitelji Stratix II.Saznat ćete o njegovim glavnim značajkama, arhitekturi, strukturi bloka i tehničkim specifikacijama kako biste shvatili kako se uklapa u napredne digitalne dizajne.Također vas prolazi kroz svoje programijske korake, aplikacije, prednosti i nedostatke, tako da možete točno vidjeti gdje i kako se ovaj uređaj može koristiti.Katalog

Što je EP2S60F672C4?

A EP2S60F672C4 je FPGA visoke gustoće iz Intela (ranije Altera), koji pripada obitelji Stratix II.Izgrađen na 90 nm, 1,2 V bakrenog SRAM procesa, pruža znatan logički kapacitet unutar FBGA paketa od 672 lopte, što ga čini idealnim za složene digitalne sustave.Kao dio EP2S serije, uređaj "60" sjedi u rasponu srednjeg do gornjeg dijela Stratix II linije, nudeći snažnu ravnotežu logičke gustoće, ugrađene memorije i I/O resursa.Poznat po snažnoj arhitekturi i pouzdanosti, ovaj FPGA ostaje pouzdan izbor u mnogim naprednim dizajnom.

Tražite EP2S60F672C4?Kontaktirajte nas kako biste provjerili trenutne zalihe, vrijeme i cijene.

EP2S60F672C4 CAD modeli

EP2S60F672C4 simbol

EP2S60F672C4

EP2S60F672C4 3D model

EP2S60F672C4

• Napredni 90 nm, 1,2 V CMOS postupak

EP2S60F672C4 izrađen je na 90 nm sve složenog bakrenog CMOS procesa koji radi na naponu jezgre od 1,2 V.Ova tehnologija omogućuje veliku brzinu, smanjenu potrošnju energije i veću gustoću logike u usporedbi sa starijim generacijama FPGA.

• ADITELJSKI LOGIČKI MODUL (ALM) arhitektura

Uređaj koristi milostinje kao svoj logički blok umjesto tradicionalnih logičkih elemenata.Ova arhitektura poboljšava korištenje resursa, omogućujući učinkovito provedbu složenijih logičkih funkcija unutar istog silicijskog područja.

• Visoka gustoća logike

S približno 60.440 logičkih elemenata (24.176 milostinja), FPGA podržava velike i sofisticirane digitalne dizajne.Ovaj visoki kapacitet čini ga prikladnim za aplikacije kao što su obrada signala, komunikacija i ugrađeni upravljački sustavi.

• TRIMATRIX ™ memorija na čipu

EP2S60F672C4 integrira tri vrste RAM blokova, (M512, M4K i M-RAM) kako bi osigurao ukupno oko 2,4 MBIT-a ugrađene memorije.Ova miks omogućuje učinkovito implementaciju malih FIFOS-a, srednjih međuspremnika i velikih sjećanja s dvostrukim portom.

• Posvećeni DSP blokovi

Uređaj uključuje 36 namjenskih DSP blokova dizajniranih za aritmetičke operacije poput multiplikacija, akumulacija i filtriranja FIR -a.Ovi blokovi povećavaju performanse u računalnim zadacima, uz štednju općih logičkih resursa.

• Integritet velike brzine I/O i signala

Podržava razne jedno-diplomske i diferencijalne I/O standarde, zajedno s dinamičkim krugom poravnanja faze (DPA).Ove značajke omogućuju stabilan, brzi prijenos podataka do 1 Gbps, osiguravajući pouzdanu komunikaciju s vanjskim komponentama.

• Bogata podrška vanjskog memorijskog sučelja

FPGA je kompatibilna s DDR, DDR2, QDR II, RLDRAM II i ostalim memorijskim standardima.Podrška ugrađenog sučelja pojednostavljuje dizajn ploče i postiže visoku propusnost podataka za aplikacije intenzivne memorije.

• Fleksibilno upravljanje satom

Do 12 PLL-a na čipu omogućuju množenje sata, podjelu, pomicanje faza i prebacivanje bez glitch-a.Možete fino prilagoditi domene sata i smanjiti podrhtavanje, podržavajući unutarnje frekvencije sata do 500–550 MHz.

• Bitstream enkripcija i rekonfiguracija

EP2S60F672C4 podržava AES-ove bitstream enkripcije za osiguranje intelektualnog vlasništva.Također nudi mogućnost daljinske rekonfiguracije, omogućavajući ažuriranja na terenu bez zamjene uređaja.

Dijagram blokaza stratix II

Dijagram blokaza Stratix II, kao što je prikazano za EP2S60F672C4, ilustrira unutarnji raspored logičkih, memorijskih i DSP resursa koji tvore jezgru FPGA.Blokovi logičkih niza (laboratoriji) raspoređeni su u redovnoj mreži, okruženi ugrađenim stupovima RAM-a i DSP-a, koji pružaju brze aritmetičke i mogućnosti skladištenja na čipu.Periferni I/O elementi i mreže takta uokviruju ovu strukturu, omogućujući učinkovitu kontrolu prijenosa podataka i vremena između FPGA i vanjskih uređaja.Ovaj je dijagram važan jer pomaže razumjeti kako su različiti funkcionalni blokovi fizički organizirani, omogućujući im da optimiziraju postavljanje, usmjeravanje i ukupnu performanse sustava.

Stratix II I/O Banke dijagram

Ovaj dijagram I/O banaka Stratix II ilustrira kako su ulazne/izlazne igle EP2S60F672C4 grupirane i koji električni standardi podržava svaka grupa.Svaka I/O banka dizajnirana je za obradu specifičnih razina napona, vrsta signalizacije i funkcija kao što su LVTTL, SSTL, LVDS ili ulazne standarde sata.Izgled pokazuje kako su različite banke (npr. 1, 2, 5, 6 prema 3, 4, 7, 8 itd.) Optimizirane ili za diferencijalnu signalizaciju opće namjene I/O ili velike brzine, uključujući podršku za LVD/LVPECL ulaze na rubovima.Razumijevanje ove strukture važno je prilikom dodjeljivanja igara, jer pravilan odabir banke osigurava električnu kompatibilnost, pojednostavljuje usmjeravanje ploče i maksimizira performanse FPGA u dizajnu velike brzine.

EP2S60F672C4 Specifikacije

|

Tip |

Parametar |

|

Proizvođač |

Altera/Intel |

|

Niz |

STratix® II |

|

Pakiranje |

Pladanj |

|

Status dijela |

Zastario |

|

Broj laboratorija/CLB -a |

3022 |

|

Broj logičkih elemenata/stanica |

60.440 |

|

Ukupni RAM komadići |

2.544.192 |

|

Broj I/O |

492 |

|

Napon - napad |

1.15 V ~ 1,25 V |

|

Montažni tip |

Površinski nosač |

|

Radna temperatura |

0 ° C ~ 85 ° C (TJ) |

|

Paket / slučaj |

672-bbga |

|

Paket uređaja dobavljača |

672-FBGA (27 × 27) |

|

Broj osnovnog proizvoda |

EP2S60 |

EP2S60F672C4 aplikacije

1. Digitalna obrada signala (DSP) i filtriranje

EP2S60F672C4 dobro je prikladan za implementaciju DSP funkcija visokih performansi kao što su FIR i IIR filtri, obrada FFT-a i složene aritmetičke operacije.Njegovi posvećeni DSP blokovi učinkovito obrađuju množenja i akumulacije, oslobađajući opće logičke resurse za druge zadatke.Trimatrix ™ memorija omogućuje glatko punjenje podataka i cjevovoda, što je izvrsno za obradu u stvarnom vremenu s visokim brzinama uzorka.Zbog toga je uređaj idealan za napredne aplikacije za audio, video i radarske signale.

2. Brzina komunikacija i umrežavanje

FPGA-ina I/O sučelja i dinamičko poravnavanje faze (DPA) podržavaju pouzdan, pouzdan prijenos podataka na razini gigabita.Može implementirati komunikacijske protokole i funkcije fizičkih slojeva za sustave poput usmjerivača, sklopki i međusobnih veza.Svojim velikim logičkim kapacitetom i fleksibilnim PLL-ovima, može upravljati složenim vremenskim i pretvorbom protokola između višestrukih brzih sučelja.Ove mogućnosti čine ga snažnim za telekomunikacijsku infrastrukturu i opremu za mrežu visoke širine.

3. Memorijski kontroleri i sustavi za obradu podataka

EP2S60F672C4 podržava različita vanjska memorijska sučelja, uključujući DDR, DDR2, RLDRAM II i QDR II, što ga čini idealnim za dizajniranje memorijskih kontrolera visoke opsega.Može podnijeti puferiranje podataka, stvaranje adresa i arbitražu pri velikim brzinama s minimalnom kašnjenjem.Kombinacija brzih mreža i ugrađenih RAM blokova omogućava učinkovito upravljanje velikim tokovima podataka.Zbog toga je FPGA prikladan za obradu slike, streaming videozapisa i znanstvene računalne platforme koje se oslanjaju na tešku propusnost podataka.

4. Prilagođena logika i ugrađeno ubrzanje

S preko 60 000 logičkih elemenata i bogatim upravljanjem sat, FPGA može ugostiti prilagođene hardverske akceleratore za određene algoritme.Dizajneri ga često koriste za isključivanje računalno intenzivnih zadataka iz CPU-a, kao što su šifriranje, raščlanjivanje protokola ili petlje u stvarnom vremenu.Također može integrirati više funkcionalnih blokova, što ga čini prikladnim za složene dizajne slične SOC-u.Ova fleksibilnost čini je vrijednom u aplikacijama poput industrijske automatizacije, sigurnosnih sustava i zrakoplovnih upravljačkih jedinica.

5. Platforme za prototipiranje i obrazovni razvoj

Uređaj EP2S60 obično se nalazi u FPGA razvojnim setovima koji se koriste za prototipiranje, testiranje i akademska istraživanja.Njegova ravnoteža logičkog kapaciteta, I/O broja i DSP mogućnosti omogućavaju inženjerima i studentima da implementiraju i provjere pune sustave na jednom čipu.Podržava brzu iteraciju digitalnih dizajna, omogućavajući provjeru hardvera prije nego što se obvezuje na razvoj ASIC -a.Mnoga sveučilišta i laboratoriji za istraživanje i razvoj koriste ga za podučavanje naprednog digitalnog dizajna i koncepata obrade signala.

Ep2s60f672c4 slični dijelovi

|

Specifikacija |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

Ep2s60f672i3n |

|

Obitelj / serija |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Logički elementi (LE) |

60.440 |

60.440 |

60.440 |

60.440 |

60.440 |

60.440 |

|

Milostinja |

24.176 |

24.176 |

24.176 |

24.176 |

24.176 |

24.176 |

|

Paket |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Brzina brzina |

C4 (std) |

C3 (brže) |

C5 (brže) |

C5 (brže) |

I4 (std) |

I3 (brže) |

|

Temperaturni stupanj |

Komercijalna (0 ~ 70 ° C) |

Komercijalni |

Komercijalni |

Komercijalni |

Industrijski (−40 ~ 100 ° C) |

Industrijski (−40 ~ 100 ° C) |

|

I/O igle |

492 |

492 |

492 |

492 |

492 |

492 |

|

Memorija na čipu |

2,4 mbit |

2,4 mbit |

2,4 mbit |

2,4 mbit |

2,4 mbit |

2,4 mbit |

|

Temeljni napon |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

|

Ključna razlika |

Osnovna komercijalna brzina |

C3 BESPE BIN, bez olova "N" |

Kanta za veću brzinu |

Bin veće brzine, "n" varijanta |

Industrijska temperatura, ista gustoća |

Industrijska, brža brzina, bez olova |

EP2S60F672C4 Koraci programiranja

Prije nego što u svom dizajnu možete koristiti EP2S60F672C4 FPGA, morate je pravilno konfigurirati sa svojim sastavljenim bitstreamom.Ovaj postupak uključuje pripremu programske datoteke, postavljanje hardverskog sučelja i osiguravanje da se konfiguracija ispravno učita na napajanju.

Korak 1: Stvorite i sastavite svoj dizajn

Započinjete razvojem svog logičkog dizajna pomoću Intel Quartus II softvera.Nakon dovršetka dizajna, sastavljate ga za generiranje programskih datoteka (.SOF ili .POF) posebno za EP2S60F672C4 uređaj.Proces kompilacije provjerava vremensko vrijeme, dodjele PIN -a i upotrebu resursa kako bi se osiguralo da se vaš dizajn uklapa u arhitekturu FPGA.Nakon što je sastavljena, vaš bitstream je spreman za konfiguraciju uređaja.

Korak 2: Postavite programski hardver

Zatim pripremate sučelje fizičkog programiranja između računala i FPGA ploče.Obično to uključuje povezivanje USB-Blaster ili kompatibilnog JTAG kabela na JTAG priključak uređaja.Trebali biste provjeriti da Quartus II prepoznaje programera i da je ciljni uređaj pravilno otkriven.Ovaj korak osigurava stabilnu komunikaciju prije pokretanja postupka konfiguracije.

Korak 3: Umetnite datoteku programiranja u uređaj

Pomoću alata Quartus II programera dodajete sastavljenu .SOF ili .POF datoteku i odaberite EP2S60F672C4 s detektiranog popisa uređaja.Zatim pokrećete programski slijed, tijekom kojeg se Bitstream prenosi i učitava u FPGA -ove ćelije konfiguracije SRAM -a.Trebali biste pratiti traku napretka i poruke statusa kako biste potvrdili uspješnu konfiguraciju.Nakon završetka, FPGA započinje odmah izvršavati programiranu logiku.

Korak 4: Provjerite konfiguraciju i rad

Nakon programiranja provjeravate da li uređaj funkcionira kako je predviđeno.Quartus II pruža mogućnost provjere provjere CRC -a i statusnih signala, osiguravajući da se dizajn pravilno učitava.Također možete testirati svoje I/O funkcije ili pokrenuti funkcionalnu simulaciju kako biste potvrdili ponašanje sustava.Ovaj posljednji korak osigurava da je vaš dizajn u potpunosti operativan i stabilan na hardveru.

EP2S60F672C4 Prednosti i nedostaci

Prednosti

• Visoka gustoća logike za složene dizajne

• Dobar omjer performansi i troškova

• Jednostavna migracija unutar iste obitelji

• Stabilni i zreli razvojni alati

• Dokazana pouzdanost u industrijskoj upotrebi

Nedostaci

• zastarjelo i teže izvoriti

• Veća potrošnja energije od novijeg FPGAS -a

• Nema modernog primopredajnika velike brzine

• teže zatvaranje vremena pri velikoj upotrebi

• Ograničena skalabilnost za buduće protokole

EP2S60F672C4 Dimenzije pakiranja

|

Tip |

Parametar |

|

Vrsta paketa |

672-FBGA (Fineline BGA) |

|

Veličina tijela (l × w) |

27,00 mm × 27,00 mm |

|

Ukupna visina paketa (a) |

Maks. 3,50 mm |

|

Visina suprotstavljanja (A1) |

Min 0,30 mm |

|

Debljina supstrata (A2) |

Max 3,00 mm |

|

Promjer kuglice (b) |

0,50 mm - 0,70 mm |

|

Kuglica (e) |

1,00 mm |

|

Broj kuglica |

672 |

|

Montažni stil |

Površinski nosač |

|

Opis paketa |

FBGA, 27 × 27 mm rešetka |

EP2S60F672C4 Proizvođač

EP2S60F672C4 FPGA proizvodi Korporacija alware, vodeći pionir u programabilnim logičkim uređajima.U 2015. godini Altera je stekao Inteliran, A proizvod sada spada u Intelovu programiranu grupu Solutions (PSG), koja i dalje podržava i opskrbljuje uspostavljene FPGA obitelji Altera.Intel održava liniju stratix II kao dio svog naslijeđenog portfelja proizvoda, osiguravajući dokumentaciju, podršku alata i dugoročnu dostupnost industrijskih i komunikacijskih aplikacija.

Zaključak

EP2S60F672C4 kombinira visoku logičku gustoću, fleksibilnu memorijsku arhitekturu i robusne I/O značajke za podršku složenih digitalnih sustava.Njegov ALM dizajn, TRIMATRIX ™ memorija, DSP blokovi i značajke upravljanja taktom omogućuju učinkovitu primjenu zahtjevnih aplikacija.Iako nudi dokazanu podršku pouzdanosti i zrele razvoja, suočava se s ograničenjima poput zastarjelosti i nedostatka modernih primopredajnika u usporedbi s novijim generacijama FPGA.Općenito, njegova uravnotežena performansi i svestranost čine ga solidnim izborom za obradu signala, komunikaciju, rukovanje podacima i aplikacije za prototipiranje.

Podatkovni list pdf

EP2S60F672C4 podataka:

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

Često postavljana pitanja [FAQ]

1. Može li EP2S60F672C4 raditi s modernim DDR memorijskim sučeljima?

Da, podržava sučelja DDR, DDR2, QDR II i RLDRAM II, koja pokrivaju mnoge uobičajene standarde vanjske memorije.To ga čini prikladnim za aplikacije za obradu podataka visoke širine.

2. Da li EP2S60F672C4 zahtijeva posebno rukovanje ili skladištenje?

Da, kao i ostale BGA-pakirane komponente, treba ga pohraniti u pakiranje pod nadzorom vlage i upravljati zaštitom od ESD-a.Slijedeći odgovarajuća praksa skladištenja pomaže u održavanju rješavanja leptibilnosti i pouzdanosti uređaja tijekom montaže.

3. Kako možete smanjiti potrošnju energije u EP2S60F672C4 dizajniranju?

Možete optimizirati korištenje logike, neiskorištene satove vrata, niže I/O napone gdje je to moguće i iskoristiti opcije sinteze svjesnosti u Quartusu II kako biste umanjili ukupno izvlačenje snage.

4. Koji su programski alati potrebni za EP2S60F672C4?

Trebat će vam Intel Quartus II softver za dizajn, kompilaciju i programiranje, zajedno s USB-Blaster ili kompatibilnim JTAG kabelom za konfiguriranje uređaja.

5. Podržava li EP2S60F672C4 ažuriranja na terenu ili daljinsku konfiguraciju?

Da, podržava AES-ove bitstream šifriranje i daljinsku rekonfiguraciju, omogućujući vam da sigurno ažurirate svoj sustav bez fizičkog zamjene FPGA.

Sve o LFXP6C-3FN256C rešetkama

na 2025/10/6

XC2C256-7TQ144C CPLD: PINKOUT, značajke, vodič za programiranje i podatkovni list

na 2025/10/3

Popularni postovi

-

Složeni računali s uputama: Kako su promijenili računanje?

na 8000/04/19 147782

-

USB-C pinout i značajke

na 2000/04/19 112062

-

Korištenje Xilinx Unified simulacijski primitivi: sveobuhvatni vodič za dizajn i simulaciju FPGA

na 1600/04/19 111352

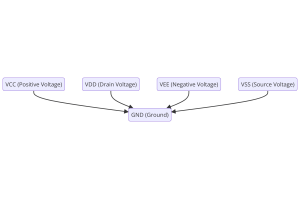

-

Naponi napajanja u elektronici: Značenje VCC, VDD, VEE, VSS i GND

na 0400/04/19 83819

-

RJ45 Vodič za priključak: pinout, ožičenje, vrste kabela i upotreba

na 1970/01/1 79639

-

Krajnji vodič za kodove u boji žice u modernim električnim sustavima

Način na koji naši električni sustavi koriste boje nisu samo za izgled.Svaka boja žice sada označava određenu funkciju, što olakšava prepoznavanje i ispravno obradu električnih komponenti tijekom u...na 1970/01/1 66999

-

Vodič za čišćenje ventila: Funkcija, simptomi, testiranje i zamjena za optimalne performanse motora

Ventil za čišćenje ključni je dio sustava automobila koji pomaže u održavanju zraka čistim upravljanjem parima goriva prije nego što mogu pobjeći u atmosferu.To ne samo da pomaže okolišu smanjenjem...na 1970/01/1 63124

-

Kvaliteta (q) Faktor: jednadžbe i aplikacije

Faktor kvalitete, ili 'q', važan je prilikom provjere koliko dobro induktori i rezonatori rade u elektroničkim sustavima koji koriste radio frekvencije (RF).'Q' mjeri koliko dobro krug minimizira g...na 1970/01/1 63062

-

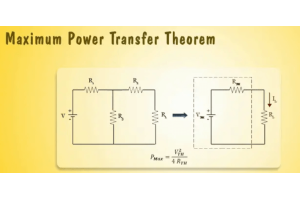

Postizanje vršnih performansi s maksimalnim teoremom prijenosa snage

Teorem maksimalnog prijenosa napajanja objašnjava kako energija iz izvora, poput baterije ili generatora, teče do povezanog opterećenja.Pokazuje točan uvjet u kojem opterećenje prima najviše snage....na 1970/01/1 54097

-

Specifikacije i kompatibilnost A23

A23 baterija je mala baterija u obliku cilindra s visokim naponom.Također se naziva 23A, 23AE ili MN21, radi na 12 volti i mnogo više od AA ili AAA baterija.Njegov poseban dizajn čini ga s...na 1970/01/1 52215