EPM7064STC100-7 CPLD: značajke, aplikacije i vodič za programiranje u sustavu

EPM7064STC100-7 snažan je čip iz Intelove serije Max® 7000S, dizajniran za rukovanje složenim zadacima u elektroničkim uređajima.Ovaj vodič raspravlja o glavnim značajkama i uporabi EPM7064STC100-7, naglašavajući njegovu sposobnost da se lako reprogramira, njegov brzi rad i fleksibilni dizajn.Idealno za mnoge različite tehnologije, od malih naprava do velikih industrijskih strojeva, ovaj čip je ključni komad za izgradnju naprednih digitalnih krugova.Katalog

EPM7064STC100-7 Opis

A EPM7064STC100-7 složen je programabilni logički uređaj (CPLD) iz Intelove serije Max® 7000S.Ima 64 makrocele i 1.250 vrata, koja pomažu u izgradnji složenih digitalnih krugova.Ovaj čip radi maksimalnom brzinom od 166,7 MHz, s kašnjenjem signala od 7,5 nanosekundi (NS).Ima 68 ulaznih/izlaznih (I/O) igle koje djeluju s logikom 3.3V i 5V, što olakšava upotrebu u različitim krugovima.Ključna značajka je njegova 5,0V programabilnost u sustavu (ISP) putem JTAG sučelja (IEEE 1149.1).To znači da ga možete reprogramirati bez uklanjanja iz kruga, olakšavajući testiranje i ažuriranja.Dolazi u 100-pinskom tankom četverostranom paketu (TQFP), koji je kompaktni, površinski montirani paket.Ovaj CPLD koristi se u ugrađenim sustavima, digitalnoj obradi signala, komunikacijskim uređajima i industrijskoj automatizaciji.

Pružamo visokokvalitetne komponente i prilagođene usluge, tako da je najbolje položiti svoj skupni redoslijed s nama za pouzdana CPLD rješenja.

EPM7064STC100-7

• Logika visoke gustoće: EPM7064STC100-7 dizajniran je sa 64 makrocele i 1.250 upotrebljivih vrata, što ga čini vrlo prikladnim za implementaciju složenih logičkih funkcija u digitalnim krugovima.Ova arhitektura visoke gustoće omogućava stvaranje zamršenih logičkih dizajna uz održavanje učinkovitosti u programibilnim logičkim operacijama.Dobro optimizirana struktura makrocelije osigurava učinkovito korištenje raspoloživih resursa, podržavajući napredne kombinacijske i uzastopne logičke implementacije.

• Brzi izvedba: Izgrađen za veliku preradu, EPM7064STC100-7 djeluje s maksimalnom unutarnjom frekvencijom od 166,7 MHz, što omogućava brzo izvršavanje logičkih funkcija.Njegovo kašnjenje širenja od 7,5 ns osigurava minimalnu latenciju.Ova sposobnost brzog prebacivanja povećava sposobnost uređaja da učinkovito obradi brze obrade podataka, kondicioniranje signala i kontrolne zadatke, što ga čini pouzdanim izborom za zahtjevne digitalne sustave.

• Svestrani I/O: Sa 68 programabilnih ulaznih/izlaznih igle, EPM7064STC100-7 nudi izuzetnu fleksibilnost za integraciju u različite dizajne kruga.Podržavajući i 3,3 V i 5V logičke razine, omogućava besprijekornu kompatibilnost s različitim naponima sustava, eliminirajući potrebu za dodatnim miješalicama razine napona.Ova prilagodljivost čini ga dobro prilagođenim za primjene u okruženjima mješovitog napona, osiguravajući široku primjenjivost ugrađenih sustava, industrijskih kontrola i komunikacijskih mreža.

• Programabilnost u sustavu (ISP): Jedna od prednosti EPM7064STC100-7 je njegova 5,0V programabilnost u sustavu (ISP), olakšana IEEE STD.1149.1 JTAG sučelje.Ova značajka omogućava reprogramiranje i izmjenu logičkih funkcija bez otpuštanja ili fizičkog uklanjanja uređaja, pojednostavljenja održavanja, uklanjanja pogrešaka i iterativnog razvoja.Mogućnost ISP -a smanjuje zastoj i poboljšava fleksibilnost ažuriranja firmvera, što ga čini neprocjenjivim za dinamične i rekonfigurabilne digitalne dizajne.

EPM7064STC100-7 CAD modeli

EPM7064STC100-7 simbol

EPM7064STC100-7

EPM7064STC100-7 3D model

EPM7064STC100-7 Blok dijagram

A EPM7064STC100-7 Blok dijagram pokazuje kako su logički elementi čipa povezani i kontrolirani.Ima četiri bloka logičkog niza (laboratorij), označen A, B, C i D, svaki sadrži 16 makrocela.Ove makrocele obavljaju logičke funkcije i povezuju se putem programiranog niza interkonektiranja (PIA), što omogućava fleksibilno usmjeravanje signala.Svaki je laboratorij povezan s upravljačkim blokom I/O, rukovanje do 16 ulaznih/izlaznih igle po laboratoriju.Dijagram također prikazuje globalne kontrolne signale (GCLK1, GCLK2, OE1 i GCLRN) koji pomažu u upravljanju funkcijama za zglob i resetiranje za čip.Neka logička vrata obrađuju te signale prije nego što dođu do različitih dijelova sustava.Dizajn EPM7064STC100-7 omogućava ga da se koristi u različitim programibilnim logičkim aplikacijama, poput državnih strojeva, dekodiranja adresa i drugih prilagođenih digitalnih krugova.Njegove fleksibilne međusobne veze osiguravaju učinkovit protok signala i pouzdan rad.

EPM7064STC100-7 Specifikacije

|

Tip |

Parametar |

|

Proizvođač |

Altera/Intel |

|

Niz |

Max® 7000s |

|

Pakiranje |

Pladanj |

|

Status dijela |

Zastario |

|

Programirajuća vrsta |

U sustavu programibilno |

|

Vrijeme odgode tpd (1) max |

7,5 ns |

|

Napon napona - unutarnji |

4.75V ~ 5.25V |

|

Broj logičkih elemenata/blokova |

4 |

|

Broj makrocela |

64 |

|

Broj vrata |

1250 |

|

Broj I/O |

68 |

|

Radna temperatura |

0 ° C ~ 70 ° C (TA) |

|

Montažni tip |

Površinski nosač |

|

Paket / slučaj |

100-tqfp |

|

Paket uređaja dobavljača |

100-TQFP (14x14) |

|

Broj osnovnog proizvoda |

EPM7064 |

Slijed EPM7064STC100-7

EPM7064STC100-7, dio obitelji MAX 7000S CPLD, slijedi šestostepeni niz programiranja u sustavu (ISP) kako bi se osigurala ispravna konfiguracija.Ovaj postupak omogućuje vam programiranje uređaja bez uklanjanja s pločice.Proces ISP -a uključuje prebacivanje uputa, adresa i podataka putem TDI (test podataka) PIN -a dok dohvaćate odgovore putem TDO (Test Data Out) PIN.

Prva faza, Unesite ISP, osigurava da I/O PIN -ovi glatko prijeđu iz korisničkog načina na ISP način i zahtijeva otprilike 1 ms.Nakon toga slijedi Provjeriti ID, gdje se čita silicijski ID uređaja kako bi se potvrdio ispravan cilj.Dalje, Rasuta brisanje Pomicanje faze u uputama za brisanje i primjenjuje impuls od 100 ms brisanja, čišćenje svih postojećih podataka u stanicama EEPROM -a.A Program Slijedi faza, gdje se adrese i podaci uzastopno prebacuju u uređaj, primjenjujući programski impuls za konfiguriranje EEPROM ćelija.Svaka adresa mora biti programirana pojedinačno, čineći ovaj korak dugotrajno ovisno o broju EEPROM ćelija u uređaju.

Jednom kada je programiranje završeno, Provjeriti Stage osigurava da su podaci pravilno pohranjeni.Ovdje se čitaju impulsi na EEPROM stanice, a dohvaćeni podaci se uspoređuju s očekivanim vrijednostima.Ako se nađu odstupanja, možda će biti potrebno reprogramiranje.Napokon, Izlaz ISP Stadija osigurava da I/O PIN -ovi prijelaz natrag u korisnički način, zahtijevajući još 1 ms.Na ukupno vrijeme programiranja ili provjere utječu dva glavna faktora: vrijeme pulsa, potrebno za brisanje EEPROM -a, programiranje i rad čitanja i vrijeme prebacivanja, što ovisi o frekvenciji TCK (testni sat) i broju ciklusa potrebnih za prijenos uputa, adrese i podataka.Budući da različiti uređaji koji imaju ISP imaju različit broj EEPROM ćelija, i ukupno fiksna i varijabilna vremena jedinstvena su za svaki uređaj.Ukupno ISP vrijeme može se izračunati kao funkcija frekvencije TCK, broja ciljnih uređaja i arhitekture EEPROM -a.

EPM7064STC100-7 aplikacije

Ugrađeni sustavi

EPM7064STC100-7 široko se koristi u ugrađenim sistemskim aplikacijama, gdje služi kao fleksibilno programibilno logičko rješenje za kontrolu različitih perifernih uređaja, signala za obradu i implementaciju prilagođenih protokola.Njegova sposobnost sučelja s mikrokontrolerima i senzorima omogućava optimizaciju performansi sustava uz održavanje kompaktnog otiska.Svojim brzim radom i malom potrošnjom energije, odličan je izbor za ugrađene aplikacije koje zahtijevaju pouzdanost i učinkovitost.

Digitalna obrada signala (DSP)

U digitalnoj obradi signala EPM7064STC100-7 igra ulogu u implementaciji filtera, modulacije signala i različitim matematičkim funkcijama.Njegove brzine brzine i nisko kašnjenje širenja čine ga prikladnim za rukovanje zadacima visokofrekventne obrade podataka, osiguravajući minimalnu latenciju u pretvorbi i manipulaciji signala.Obično se koristi u audio obradi, telekomunikacijama i radarskim sustavima.

Komunikacije podataka

EPM7064STC100-7 uvelike se koristi u mrežnim i podatkovnim komunikacijskim sustavima zbog svoje sposobnosti rukovanja logičkim operacijama poput usmjeravanja podataka, punjenja i korekcije pogrešaka.Njegove programibilne I/O mogućnosti omogućuju mu prilagodbu različitim komunikacijskim protokolima, što ga čini vrijednom komponentom u Ethernet sklopcima, usmjerivačima i telekomunikacijskoj infrastrukturi.Njegova podrška za programiranje u sustavu (ISP) također omogućuje ažuriranja na terenu, poboljšavajući prilagodljivost u okruženjima dinamičkog umrežavanja.

Industrijska automatizacija

Industrijske aplikacije zahtijevaju visoku pouzdanost, izdržljivost i malu potrošnju energije, čineći EPM7064STC100-7 preferirani izbor za programibilne logičke kontrolere (PLC), sustave za upravljanje motorom i automatiziranu opremu za testiranje.Sa svojom programiranjem u sustavu u sustavu JTAG, on pruža mogućnost usavršavanja procesa automatizacije bez potrebe za fizičkim uklanjanjem ili redizajnom.Njegova svestranost u kompatibilnosti napona također je čini prikladnom za povezivanje sa širokim rasponom senzora i pokretača koji se koriste u industrijskim postavkama.

EPM7064STC100-7 slični dijelovi

EPM7064STC100-7 Prednosti

Programabilnost u sustavu (ISP)

Jedna od najvećih prednosti EPM7064STC100-7 je njegova sposobnost da se reprogramira dok je još uvijek montirana u sustavu.To eliminira potrebu za uklanjanjem čipa za ažuriranja, smanjenja vremena održavanja i poboljšanja učinkovitosti.Možete implementirati izmjene dizajna bez prekida proizvodnje, što ga čini isplativim rješenjem za dugoročne projekte.

Performanse velike brzine

Uređaj podržava visoku internu radnu frekvenciju do 166,7 MHz, omogućujući brzu obradu podataka i vrijeme odziva.To ga čini idealnim za aplikacije koje zahtijevaju obradu signala, kontrolu logike i povezivanje brzih brzina, osiguravajući glatkiji i pouzdaniji rad sustava.

Svestrana I/O podrška

S do 68 konfiguriranih I/O pinova i kompatibilnosti s više razina napona (3,3 V, 5V i tolerantne opcije za 2,5 V, 3.3V i 5V), EPM7064STC100-7 nudi fleksibilnost u dizajnu sustava.Omogućuje besprijekornu integraciju u različite krugove i podržava okruženje mješovitih napona, smanjujući probleme s kompatibilnošću s drugim komponentama.

Pouzdan rad u okruženjima

Dizajniran da funkcionira unutar temperaturnog raspona od 0 ° C do 70 ° C, EPM7064STC100-7 osigurava dosljedan i stabilan rad u različitim uvjetima.Ova pouzdanost čini ga preferiranim izborom za aplikacije u kojima je potrebna stabilnost okoliša, poput industrijske automatizacije, telekomunikacija i ugrađenih upravljačkih sustava.

EPM7064STC100-7 DIJAGRAM PAKET

EPM7064STC100-7 je CPLD (složeni programabilni logički uređaj) iz serije Altera Max 7000S, smješten u 100-pinskom tankom kvadratnom paketu (TQFP-100).Ova vrsta paketa dizajnirana je za površinske montirane aplikacije, nudeći ravnotežu visoke gustoće pinova i kompaktne veličine.A dijagram otičanja Slijedi shemu numeriranja u smjeru suprotnom od kazaljke na satu, s pin 1 smještenim u gornjem lijevom kutu paketa.Krećući se u smjeru suprotnom od kazaljke na satu, prvih 25 igara zauzimaju lijevu stranu, igle 26 do 50 postavljeni su duž donjeg ruba, igle 51 do 75 nastavljaju se duž desne strane, a igle 76 do 100 raspoređene su duž gornjeg ruba.A TQFP-100 paket Sadrži tanke potencijale koji se protežu prema van sa sve četiri strane ravnog, kvadratnog tijela.Ovaj dizajn povećava kompatibilnost s površinskim montiranjem uz održavanje odgovarajućeg razmaka za lagano lemljenje i montažu.Olovo nagib (udaljenost između susjednih igle) je obično 0,5 mm, optimizirajući integritet signala, istovremeno minimizirajući ukupni otisak.

EPM7064STC100-7 Proizvođač

EPM7064STC100-7 je CPLD (složeni programabilni logički uređaj) koji je izvorno razvila AlterA, poluvodička kompanija poznata po svojim programibilnim logičkim rješenjima.U 2015. godini, Inteliran stečena Altera, integrirajući svoje linije proizvoda FPGA i CPLD u Intelovu programabilnu grupu Solutions (PSG).Od tada je EPM7064STC100-7 označen pod Intelom, iako je označen kao zastarjeli.Intel je kao proizvođač održavao naslijeđenu podršku za CPLDS serije Max® 7000S, uključujući ovaj model, istovremeno postupno prebacujući svoj fokus na moderne FPGA i programabilne logičke tehnologije.

Zaključak

EPM7064STC100-7 okuplja složene funkcije, brze performanse i jednostavna ažuriranja u jednom čipu, što dokazuje svoju vrijednost u izazovima digitalnih postavki.Ovaj je vodič pokazao kako djeluje, za što se koristi i kako se uklapa u razne elektroničke sustave.Pomaže u tome da uređaji rade glatko i učinkovito, dokazujući da je još uvijek vrlo koristan za mnoge aplikacije.Ovaj vodič pruža jasan prikaz kako EPM7064STC100-7 može pomoći učinkovito poboljšati elektroničke nacrte i operacije sustava.

Podatkovni list pdf

EPM7064STC100-7 podataka:

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

Često postavljana pitanja [FAQ]

1. Kako kašnjenje širenja 7,5NS odgode EPM7064STC100-7 performansi utjecajnog kruga?

Kašnjenje razmnožavanja 7,5NS osigurava obradu signala niske kašnjenja, što ovaj CPLD čini prikladnim za brze aplikacije kao što su digitalna obrada signala (DSP), komunikacijski sustavi i industrijska automatizacija koja zahtijevaju preciznu kontrolu vremena.

2. Može li se EPM7064STC100-7 programirati pomoću modernih alata za razvoj?

Da, može se programirati pomoću Intel -ovog softvera Quartus II (ranije Altera Quartus) zajedno s odgovarajućim programerom JTAG -a.Međutim, podrška za starije CPLD-ove poput EPM7064STC100-7 može biti ograničena u novijim verzijama kvartusa, tako da ćete možda trebati koristiti naslijeđene verzije poput Quartus II 13.0 SP1, koje i dalje podržavaju uređaje serije Max® 7000S.

3. Podržava li EPM7064STC100-7 okruženja mješovitih napona?

Da, podržava i 3,3 V i 5V logičke razine, što ga čini kompatibilnim sa širokim rasponom digitalnih krugova.Ova je fleksibilnost korisna za povezivanje naslijeđenih 5V komponenti s modernim 3.3V sustavima bez dodatnog kruga za promjenu razine.

4. Koja je najbolja metoda za rješavanje problema EPM7064STC100-7 temeljenog na dizajnu?

Za rješavanje problema, za praćenje signala možete koristiti Quartus SignalTap II logički analizator ili vanjske osciloskope i logičke analizere.Ako uklanjanje pogrešaka JTAG programiranja, osigurajte da su TDI, TDO, TCK i TMS veze točni i da koristite kompatibilni USB blaster ili programer ByteBlasterMV.

5. Mogu li programirati EPM7064STC100-7 bez uklanjanja s moje ploče?

Da.Programiranje u sustavu 5.0V (ISP) putem JTAG (IEEE 1149.1) omogućuje vam reprogramiranje uređaja dok ostaje u sustavu.Zbog toga je ažuriranja, uklanjanje pogrešaka u firmveru i testiranje mnogo učinkovitijim u usporedbi s tradicionalnim CPLD -ovima.

Kompletni vodič za 10K otpornik: Kod boja, aplikacije i korištenja kruga

na 2025/03/10

Kondenzatori u odnosu na baterije: Što je najbolje za vaše potrebe za energijom?

na 2025/03/7

Popularni postovi

-

Složeni računali s uputama: Kako su promijenili računanje?

na 8000/04/18 147769

-

USB-C pinout i značajke

na 2000/04/18 111998

-

Korištenje Xilinx Unified simulacijski primitivi: sveobuhvatni vodič za dizajn i simulaciju FPGA

na 1600/04/18 111351

-

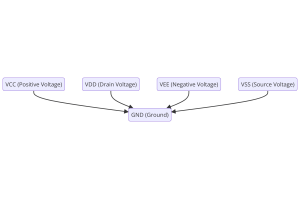

Naponi napajanja u elektronici: Značenje VCC, VDD, VEE, VSS i GND

na 0400/04/18 83765

-

RJ45 Vodič za priključak: pinout, ožičenje, vrste kabela i upotreba

na 1970/01/1 79558

-

Krajnji vodič za kodove u boji žice u modernim električnim sustavima

Način na koji naši električni sustavi koriste boje nisu samo za izgled.Svaka boja žice sada označava određenu funkciju, što olakšava prepoznavanje i ispravno obradu električnih komponenti tijekom u...na 1970/01/1 66956

-

Vodič za čišćenje ventila: Funkcija, simptomi, testiranje i zamjena za optimalne performanse motora

Ventil za čišćenje ključni je dio sustava automobila koji pomaže u održavanju zraka čistim upravljanjem parima goriva prije nego što mogu pobjeći u atmosferu.To ne samo da pomaže okolišu smanjenjem...na 1970/01/1 63098

-

Kvaliteta (q) Faktor: jednadžbe i aplikacije

Faktor kvalitete, ili 'q', važan je prilikom provjere koliko dobro induktori i rezonatori rade u elektroničkim sustavima koji koriste radio frekvencije (RF).'Q' mjeri koliko dobro krug minimizira g...na 1970/01/1 63035

-

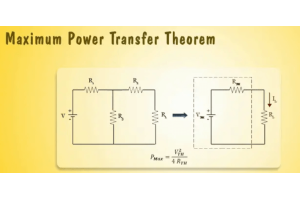

Postizanje vršnih performansi s maksimalnim teoremom prijenosa snage

Teorem maksimalnog prijenosa napajanja objašnjava kako energija iz izvora, poput baterije ili generatora, teče do povezanog opterećenja.Pokazuje točan uvjet u kojem opterećenje prima najviše snage....na 1970/01/1 54095

-

Specifikacije i kompatibilnost A23

A23 baterija je mala baterija u obliku cilindra s visokim naponom.Također se naziva 23A, 23AE ili MN21, radi na 12 volti i mnogo više od AA ili AAA baterija.Njegov poseban dizajn čini ga s...na 1970/01/1 52177