LFEC3E-3Q208C FPGA Pregled: značajke, aplikacije, programiranje i specifikacije

U ovom ćete članku saznati o LFEC3E-3Q208C, FPGA iz rešetke Semiconductor.Vidjet ćete o čemu se radi, glavne značajke koje nudi i zašto je korisno za mnoge dizajne srednjeg raspona.Sadržaj vas također prolazi kroz svoje specifikacije, aplikacije i postupak programiranja korak po korak, zajedno sa svojim detaljima o prednostima, nedostacima i proizvođačima.Katalog

Što je LFEC3E-3Q208C?

A LFEC3E-3Q208C je ekonomičan niz na terenu koji se može nadograditi na terenu (FPGA) iz rešetke Semiconductor, osmišljen kao dio obitelji Latticeec (ekonomija).Ova je obitelj razvijena za pružanje programibilnih logičkih rješenja koja uravnotežuju pristupačnost s pouzdanim performansama za glavne dizajne.Unutar hijerarhije Latticeec sjedi u srednjem rasponu, nudeći oko 3000 logičkih elemenata i učinkovitu potrošnju energije, premošćivši jaz između manjih uređaja za unos i većih, više intenzivnih modela resursa.Šira serija LatticeECP/EC naglašava jeftinu programabilnost, skalabilnost i fleksibilnost u više veličina uređaja, pri čemu se varijanta EC fokusirala na performanse usmjerene na ekonomiju.

Tražite LFEC3E-3Q208C?Kontaktirajte nas kako biste provjerili trenutne zalihe, vrijeme i cijene.

LFEC3E-3Q208C

• Logički resursi

Uređaj integrira oko 3.100 logičkih elemenata organiziranih u 384 bloka, što mu daje dovoljno kapaciteta za dizajn srednjeg raspona.Ova ravnoteža resursa čini ga prikladnim za kontrolnu logiku, obradu signala i ugrađene aplikacije bez pretjeranih troškova.

• Programirani I/O

S do 145 programabilnih ulaznih/izlaznih igle podržava široku paletu mogućnosti povezivanja.Ovi I/OS kompatibilni su s više standarda kao što su LVCMOS, LVTTL, LVDS, PCI i SSTL, omogućavajući fleksibilnu integraciju sustava.

• Ugrađena memorija

FPGA uključuje namjenski blok RAM-a (EBR) i distribuirane RAM-ove resurse, pružajući učinkovito skladištenje na čipu.To omogućava implementaciju puferiranja podataka, tablica pretraživanja ili male ugrađene uspomene izravno unutar uređaja.

• Upravljanje satom

Sadrži do četiri integrirana PLL -ova, nudeći množenje frekvencije, podjelu i pomicanje faza.To omogućava preciznu kontrolu vremena i sinkronizaciju dizajna brzih brzina.

• Podrška za DDR memoriju

Uređaj uključuje hardversku podršku za DDR sučelja, sposobna za pokretanje DDR400 (200 MHz).To ga čini praktičnim za dizajne koji zahtijevaju vanjski pristup memoriji velike brzine.

• Učinkovitost napajanja

Radeći s jezgrom 1,2 V, FPGA minimizira ukupnu potrošnju energije sustava.Njegov dizajn male snage idealan je za prijenosne ili energetski osjetljive aplikacije.

• Značajke na razini sustava

Ugrađene funkcije kao što su IEEE 1149.1 granično skeniranje, logička analiza na čipu (ISPtracy) i SPI Flash Flash sučelje pojednostavljuju testiranje i uklanjanje pogrešaka.Ove značajke smanjuju vrijeme razvoja i poboljšavaju pouzdanost dizajna.

• Razvojna podrška

Podržan od iplever Design Suite, uređaj ima koristi od automatizirane sinteze, alatima za mjesto i rute.Također možete koristiti IPplevercore IP blokove za ubrzanje uobičajenih funkcija i skraćivanje vremena na tržište.

LATTICEECP/EC BLOK BLOK DIGIGRAM

Blok dijagram obitelji LatticeECP/EC (uključujući LFEC3E-3Q208C) pokazuje kako je FPGA izgrađena i kako njegovi dijelovi rade zajedno.Programirajuće I/O stanice (PICS) postavljaju se oko rubova kako bi se čip povezivao s vanjskim uređajima, podržavajući mnoge signalne standarde.Iznutra, programibilne funkcionalne jedinice (PFUS) upravljaju logičkim operacijama, s nekim uparenim u ugrađeni blok RAM -a (EBR) za pohranjivanje podataka, a drugi fokusirani samo na logiku.SYSClock PLLS upravljaju signalima takta kako bi dizajn mogao raditi pravom brzinom i vremenom.Port SysConfig i JTAG Port omogućuju vam lako programiranje, testiranje i uklanjanje pogrešaka FPGA.Ovaj izgled daje fleksibilnost, pouzdane performanse LFEC3E-3Q208C i jednostavnu integraciju u dizajnu osjetljivih na troškove.

Rešetka

Kriška u obitelji LatticeECP/EC, kao u LFEC3E-3Q208C, osnovna je logička jedinica koja kombinira blokove LUT4 & nose blokove za obavljanje logičkih i aritmetičkih operacija.Svaka kriška također uključuje flip-flops/zasune za pohranu podataka i omogućavanje uzastopne logike, s multipleksima za fleksibilno usmjeravanje signala putem registara ili izravno.Ova je struktura važna jer daje FPGA brzinu, fleksibilnost i učinkovitost za obradu jednostavnih i složenih digitalnih dizajna.Sljedeća tablica sažima opise signala na kriški, uključujući njihove funkcije, vrste, imena signala i svrhe.

|

Funkcija |

Tip |

Signalna imena |

Opis |

|

Ulazni |

Signal podataka |

A0, B0, C0, D0 |

Ulazi u LUT4 |

|

Ulazni |

Signal podataka |

A1, B1, C1, D1 |

Ulazi u LUT4 |

|

Ulazni |

Višenamjenski |

M0 |

Višenamjenski ulaz |

|

Ulazni |

Višenamjenski |

M1 |

Višenamjenski ulaz |

|

Ulazni |

Upravljački signal |

Ce |

Sat Omogući |

|

Ulazni |

Upravljački signal |

Lsr |

Lokalni set/resetiranje |

|

Ulazni |

Upravljački signal |

Clk |

Sat sistema |

|

Ulazni |

Inter-PFU signal |

Fcin |

Brzo nosite ušnja |

|

Izlaz |

Podatkovni signali |

F0, F1 |

LUT4 izlazni registar zaobilaznih signala |

|

Izlaz |

Podatkovni signali |

Q0, Q1 |

Registrirajte izlaze |

|

Izlaz |

Podatkovni signali |

OFX0 |

Izlaz LUT5 muxa |

|

Izlaz |

Podatkovni signali |

Ofx1 |

Izlaz Lut6, LUT7, LUT8 2 MUX, ovisno o krišci |

|

Izlaz |

Inter-PFU signal |

FCO |

Za pravo većinu PFU -a izlaz lananog lana |

LFEC3E-3Q208C Specifikacije

|

Tip |

Parametar |

|

Proizvođač |

Rešetka |

|

Napon - napad |

1.14V ~ 1.26V |

|

Ukupni RAM komadići |

56.320 |

|

Paket uređaja dobavljača |

208-PQFP (28x28) |

|

Niz |

EC |

|

Paket / slučaj |

208-bfqfp |

|

Paket |

Pladanj |

|

Radna temperatura |

0 ° C ~ 85 ° C (TJ) |

|

Broj logičkih elemenata/stanica |

3.100 |

|

Broj I/O |

145 |

|

Montažni tip |

Površinski nosač |

|

Broj osnovnog proizvoda |

Lfec3 |

LFEC3E-3Q208C aplikacije

1. Ugrađeni upravljački sustavi

LFEC3E-3Q208C dobro je prilagođen ugrađenim kontrolerima u uređaje, industrijsku automatizaciju i IoT gateways.Njegova umjerena logička gustoća i jeftini dizajn omogućuju zamjenu logike fiksne funkcije s programibilnom fleksibilnošću.To olakšava nadogradnju sustava ili prilagođavanje razvijajućim standardima bez redizajniranja hardvera.

2. DDR memorija povezivanje

S ugrađenom podrškom za DDR400 memoriju, uređaj može upravljati puferom podataka, evidentiranjem ili privremenom pohranom u aplikacijama.Ova je značajka korisna u sustavima u kojima je važna brzina vanjske memorije, ali nije potrebna potpuna performansi FPGA vrhunskog razreda.Mnogi imaju koristi od ravnoteže brzine, troškova i memorije.

3. I/O premošćivanje i pretvorba protokola

Zahvaljujući širokoj podršci za I/O standarde poput LVCMOS, LVTTL, LVDS, PCI i SSTL, FPGA je učinkovita u premošćivanju različitih digitalnih sučelja.Može se konfigurirati za prevođenje signala između podsustava, što ga čini vrijednim u dizajnu mješovite tehnologije.Ova fleksibilnost pomaže proširiti život postojećeg hardvera omogućavajući kompatibilnost s novim komponentama.

4. industrijske i infrastrukturne aplikacije

Uređaj također može poslužiti u industrijskoj i infrastrukturnoj opremi osjetljivoj na troškove, gdje su dovoljni pouzdanost i umjerene performanse.Njegova podrška za granično skeniranje, uklanjanje pogrešaka na čipu i rad male snage čine ga idealnim za sustave koji zahtijevaju učinkovitost i lako održavanje.Tipične uloge uključuju upravljačke jedinice, module sučelja i sustave za praćenje.

LFEC3E-3Q208C slični dijelovi

|

Specifikacija |

LFEC3E-3Q208C |

LFEC3E-3Q208I |

LFEC3E-3QN208C |

LFEC3E-4Q208C |

LFEC1E-3Q208C

|

LFEC6E-3Q208C

|

|

Logički elementi (LUTS) |

~ 3,1k |

~ 3,1k |

~ 3,1k |

~ 3,1k |

~ 1,5K |

~ 6,1K |

|

Logički blokovi |

384 |

384 |

384 |

384 |

192 |

768 |

|

Ugrađeni blok RAM -a (EBR) |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 18 kb |

~ 92 kb |

|

Maksimalna radna frekvencija |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 300 MHz |

~ 340 MHz |

|

I/O Broj |

145 |

145 |

145 |

145 |

112 |

145 |

|

Paket |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

|

Temeljni napon |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

|

Temperaturni raspon |

0 ° C do +70 ° C |

–40 ° C do +85 ° C |

0 ° C do +70 ° C |

0 ° C do +70 ° C |

0 ° C do +70 ° C |

0 ° C do +70 ° C |

|

Usklađenost / vrsta paketa |

Standard |

Industrijski |

Bez olova (QN) |

Varijanta (q) |

Standard |

Standard |

|

Prijava |

Srednja gustoća, opća namjera |

Isto kao LFEC3E, ali industrijska upotreba |

Isto kao LFEC3E, ali paket usklađen |

Ista obitelj, laka migracija |

Opcija troškova niske gustoće |

Nadogradnja veće gustoće |

Koraci programiranja LFEC3E-3Q208C

Prije nego što započnete programiranje LFEC3E-3Q208C, važno je pripremiti prave alate i razumjeti protok dizajna do konfiguracije uređaja.Svaki se korak gradi na prethodnom, pa će pažljiva pažnja osigurati nesmetan postupak programiranja.

1. Pripremite programiranje hardvera i softvera

Započinjete instaliranjem rešetke Diamond programera ili ISPVM sustava, koji su službeni alati za ovaj FPGA.Zatim postavite kabel za programiranje JTAG-a kao što je HW-USBN-2B i provjerite jesu li upravljački programi pravilno instalirani.Ovaj korak osigurava da je vaše računalo spremno komunicirati s ciljnim uređajem bez pogrešaka u vezi.

2. Provedite svoj dizajn u razvojnom softveru

Zatim stvorite novi projekt u rešetki Diamond i odaberite LFEC3E-3Q208C kao svoj ciljni uređaj.Zatim dodajete svoje verilog ili VHDL izvorne datoteke, primjenjujete PIN zadatke i definirate ograničenja vremena.Jednom kada to učinite, sintetizirate dizajn, izvodite mjesto i ruti i na kraju generirate datoteku Bitstream (.bit ili .jed) koja će se koristiti za programiranje.

3. Postavite ploču i veze

Sada spojite JTAG kabel na svoju FPGA ploču, osiguravajući da je priključak na zemlju sigurna prije pričvršćivanja signalnih linija.Potvrdite da su otpornici povlačenja i padanja pravilno na mjestu, posebno na TCK i otvorenim linijama.Ako vaša ploča ima dodatne upravljačke igle poput Erase ili Ispen, morate ih pravilno konfigurirati kako biste spriječili slučajne resetiranje tijekom programiranja.

4. Programirajte uređaj

Uz spreman hardver, pokrenite alat za programiranje i odaberite svoj spojeni kabel.Učitajte generiranu datoteku BitStream i odaberite odgovarajući način, obično JTAG, ovisno o vašem postavljanju.Pokrenite postupak programiranja, a alat će konfigurirati FPGA prilikom provjere jesu li podaci pravilno napisani.

5. Provjerite i uklanjam pogrešku konfiguracije

Nakon programiranja provjerite završene ili init igle na vašoj ploči kako biste potvrdili da je FPGA uspješno konfigurirala.Ako je potrebno, upotrijebite logički analizator ISPtracy ili značajke graničnog skeniranja za testiranje funkcionalnosti i potvrđivanje ponašanja signala.Možete ponoviti ciklus dizajna i programiranja kad god su potrebne promjene, osiguravajući da se vaš projekt rafinira korak po korak.

LFEC3E-3Q208C Prednosti i nedostaci

Prednosti

• Mala potrošnja energije, pogodna za energetski osjetljive na dizajne

• isplativi u usporedbi s FPGAS-om višeg razreda

• Jednostavna kolica s alatima s lakšim krivuljom učenja

• Područje koje se može konfigurirati za ažuriranja nakon implementacije

• Kompaktni paket s dobrom ravnotežom resursa

Nedostaci

• Ograničeni učinak u usporedbi s većim FPGAS -om

• Niži logički i memorijski kapacitet od visokog razreda

• Manje IP jezgara trećih strana i podrška ekosustavu

• Alats nedostaju napredne značajke glavnih dobavljača

• Nije prikladno za sučelja ultra velike brzine

LFEC3E-3Q208C Dimenzije pakiranja

|

Tip |

Parametar |

|

Vrsta paketa |

208-PQFP (plastični quad ravni paket) |

|

Veličina tijela |

28 mm × 28 mm |

|

Nagib |

0,5 mm |

|

Visina paketa (max) |

~ 3,4 mm |

|

Brojanje olova |

208 igle |

|

Stil paketa |

Glupovi (Quad) |

|

Montažni tip |

Površinski nosač |

|

Kodeks predmeta |

BFQFP-208 |

|

Paket dobavljača |

Pladanj |

LFEC3E-3Q208C Proizvođač

LFEC3E-3Q208C proizvodi Rešetka Pomiconductor Corporation , američka tvrtka sa sjedištem u Hillsborou, Oregon.Osnovana 1983. godine, rešetka je specijalizirana za razvoj nizova s niskim energijom, ekonomičnim poljama na terenu (FPGAS) i srodnim rješenjima.Tvrtka se fokusira na omogućavanje aplikacija na komunikaciji, računarstvu, potrošačkoj elektronici, industrijskom i automobilskom tržištu.Poznata po svojoj inovaciji u energetski učinkovitim programibilnim uređajima, rešetka se etablirala kao ključni igrač u industriji FPGA, posebno po dizajnu koji zahtijevaju kompaktne faktore oblika, smanjenu potrošnju energije i visoku pouzdanost.

Zaključak

LFEC3E-3Q208C nudi dobru mješavinu niske cijene, male potrošnje energije i dovoljno logike i memorije za projekte srednjeg raspona.Podržava mnoge I/O standarde, ima ugrađeni RAM i PLLS, a može raditi s DDR400 memorijom, što ga čini korisnim za kontrolu, sučelje i industrijske zadatke.Programiranje je jednostavno s alatima za rešetke, a dodatne značajke za uklanjanje pogrešaka pomažu u testiranju.Iako ne može uskladiti brzinu i kapacitet većih FPGA -ova, to je pouzdan izbor za dizajne koji trebaju fleksibilnost, učinkovitost i pristupačne performanse.

Podatkovni list pdf

LFEC3E-3Q208C podatkovne liste:

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

Često postavljana pitanja [FAQ]

1. Podržava li LFEC3E-3Q208C velika brzina sučelja poput PCIE ili GIGABIT ETHENTET?

Ne. LFEC3E-3Q208C dizajniran je za primjenu glavnih i troškova, tako da ne uključuje izvorne serijske primopredajne brzine velike brzine.Umjesto toga, fokusira se na paralelna sučelja i podršku DDR memorije.

2. Može li se LFEC3E-3Q208C reprogramirati nakon implementacije?

Da.Kao FPGA, LFEC3E-3Q208C je u potpunosti konfigurirano, omogućavajući ažuriranja i modifikacije dizajna čak i nakon implementacije.Ova fleksibilnost smanjuje dugoročne troškove održavanja i proširuje životne cikluse proizvoda.

3. Kako se LFEC3E-3Q208C bavi uklanjanjem pogrešaka i testiranja?

Uređaj integrira granično skeniranje (IEEE 1149.1), logičku analizu na čipu (ISPtracy) i SPI podršku za bljeskalicu.Ovi ugrađeni alati pojednostavljuju uklanjanje pogrešaka i smanjuju potrebu za vanjskim hardverom za testiranje.

4. Može li LFEC3E-3Q208C proširiti životni vijek starijih hardverskih sustava?

Da, zahvaljujući širokoj I/O kompatibilnosti i mogućnostima premošćivanja protokola, može sučeljavati starije sustave s novijim komponentama, pomažući tvrtkama da prošire korisnost postojećeg hardvera.

5. Koji su programski alati potrebni za LFEC3E-3Q208C?

Programiran je pomoću rešetke Diamond programera ili ISPVM sustava.Ovi alati podržavaju unos dizajna, stvaranje bitstreama i konfiguraciju uređaja, čineći tijek rada pojednostavljen.

AD73311LARS: podatkovni list, značajke, pinout i vodič za programiranje

na 2025/08/28

EPM1270F256C4N MAX II CPLD Pregled: Značajke, specifikacije i aplikacije

na 2025/08/28

Popularni postovi

-

Složeni računali s uputama: Kako su promijenili računanje?

na 8000/04/19 147784

-

USB-C pinout i značajke

na 2000/04/19 112077

-

Korištenje Xilinx Unified simulacijski primitivi: sveobuhvatni vodič za dizajn i simulaciju FPGA

na 1600/04/19 111352

-

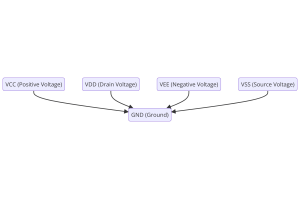

Naponi napajanja u elektronici: Značenje VCC, VDD, VEE, VSS i GND

na 0400/04/19 83844

-

RJ45 Vodič za priključak: pinout, ožičenje, vrste kabela i upotreba

na 1970/01/1 79648

-

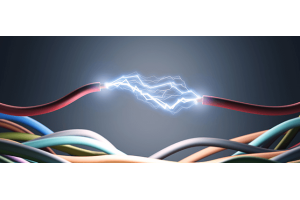

Krajnji vodič za kodove u boji žice u modernim električnim sustavima

Način na koji naši električni sustavi koriste boje nisu samo za izgled.Svaka boja žice sada označava određenu funkciju, što olakšava prepoznavanje i ispravno obradu električnih komponenti tijekom u...na 1970/01/1 67022

-

Vodič za čišćenje ventila: Funkcija, simptomi, testiranje i zamjena za optimalne performanse motora

Ventil za čišćenje ključni je dio sustava automobila koji pomaže u održavanju zraka čistim upravljanjem parima goriva prije nego što mogu pobjeći u atmosferu.To ne samo da pomaže okolišu smanjenjem...na 1970/01/1 63140

-

Kvaliteta (q) Faktor: jednadžbe i aplikacije

Faktor kvalitete, ili 'q', važan je prilikom provjere koliko dobro induktori i rezonatori rade u elektroničkim sustavima koji koriste radio frekvencije (RF).'Q' mjeri koliko dobro krug minimizira g...na 1970/01/1 63071

-

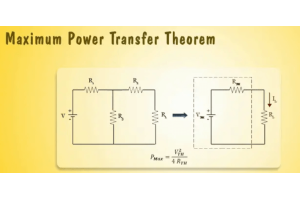

Postizanje vršnih performansi s maksimalnim teoremom prijenosa snage

Teorem maksimalnog prijenosa napajanja objašnjava kako energija iz izvora, poput baterije ili generatora, teče do povezanog opterećenja.Pokazuje točan uvjet u kojem opterećenje prima najviše snage....na 1970/01/1 54100

-

Specifikacije i kompatibilnost A23

A23 baterija je mala baterija u obliku cilindra s visokim naponom.Također se naziva 23A, 23AE ili MN21, radi na 12 volti i mnogo više od AA ili AAA baterija.Njegov poseban dizajn čini ga s...na 1970/01/1 52235