Razumijevanje LFSC3GA25E-7F900C FPGA arhitekture i ključnih funkcija

Istraživanje LFSC3GA25E-7F900C daje vam bliži uvid u to kako programabilni logički uređaji podržavaju fleksibilne digitalne sustave.Možete koristiti ovaj FPGA za organiziranje putova podataka, upravljanje signalima i izgradnju prilagođenih logičkih funkcija unutar jednog čipa.Njegov unutarnji raspored kombinira programabilne logičke ćelije, memorijske blokove i ulazne izlazne banke tako da se signali učinkovito kreću kroz uređaj.Razumijevanje načina na koji ovi odjeljci rade zajedno pomaže vam da vidite kako su složeni elektronički sustavi strukturirani.Od komunikacijskog hardvera do upravljačkih sustava, ovaj FPGA nudi praktičan način za stvaranje prilagodljivog digitalnog dizajna.Katalog

LFSC3GA25E-7F900C Pregled

LFSC3GA25E-7F900C je programabilni logički uređaj dizajniran za podršku konfigurabilnih digitalnih funkcija u ugrađenim elektroničkim sustavima.Uređaj sadrži logičku strukturu temeljenu na mreži s tisućama programabilnih elemenata, interne memorijske resurse i brojne ulazne i izlazne veze za vanjsku komunikaciju.Njegova arhitektura omogućuje implementaciju digitalnih sklopova, kontrolnih puteva i zadataka obrade signala unutar jednog čipa.Integrirane mreže za usmjeravanje povezuju logičke blokove i memorijske dijelove kako bi se podaci mogli kretati kroz uređaj na strukturiran način.Rad je podržan niskim rasponom opskrbe jezgre i paketom s velikim brojem pinova prikladnim za guste rasporede ploča.

Tražim LFSC3GA25E-7F900C.Kontaktirajte nas da provjerite trenutne zalihe, vrijeme isporuke i cijene.

Banke LFSC3GA25E-7F900C

Raspored ulaznih i izlaznih banaka koji se koristi u LFSC3GA25E-7F900C FPGA koji pokazuje kako uređaj organizira svoje programibilne I O resurse u više regija kontroliranih naponom.Osam skupina raspoređeno je oko perimetra uređaja i svaka skupina uključuje grupirane veze za VCCIO napajanje, ulaze referentnog napona označene VREF, pinove napona završetka označene VTT i uzemljenje.Ova struktura omogućuje svakoj banci rad s neovisnim električnim uvjetima tako da različiti standardi signala mogu biti podržani na odvojenim stranama uređaja.Blokovi sučelja SERDES pojavljuju se u blizini gornjih obala kako bi podržali serijske komunikacijske kanale velike brzine povezane s obližnjim IO regijama.Izgled također identificira zajedničke referentne pinove i priključke za napajanje koji definiraju način na koji vanjski signali komuniciraju s internom programibilnom logikom kroz bankiranu IO strukturu.

LFSC3GA25E-7F900C CAD model

LFSC3GA25E-7F900C Simbol

LFSC3GA25E-7F900C Otisak

LFSC3GA25E-7F900C 3D model

Značajke LFSC3GA25E-7F900C

Programabilna logika visoke gustoće

Uređaj integrira oko dvadeset pet tisuća programabilnih logičkih elemenata raspoređenih u organiziranu mrežu.Ove logičke ćelije mogu se konfigurirati za implementaciju digitalnih kontrolnih staza, kombinacijske logike i aritmetičkih operacija unutar ugrađenih sustava.

Arhitektura ugrađene memorije

Interni memorijski resursi pružaju više od jednog megabita kapaciteta pohrane za međuspremnik podataka i podržavanje logičkih operacija.Ovi memorijski blokovi raspoređeni su po cijelom uređaju tako da logički sklopovi mogu pristupati podacima lokalno bez dugih puteva usmjeravanja.

Fleksibilno povezivanje ulaza i izlaza

Do tri stotine sedamdeset osam ulaznih i izlaznih veza omogućuje uređaju interakciju sa senzorima, komunikacijskim sučeljima i drugim digitalnim komponentama.Struktura pinova podržava višestruke električne standarde u neovisnim IO bankama.

Integrirani resursi za upravljanje satom

Unutarnji blokovi za upravljanje satom pomažu u distribuciji vremenskih signala kroz programabilnu logičku strukturu.Ovi resursi održavaju sinkronizirano vrijeme signala tako da se digitalne operacije odvijaju u urednom i predvidljivom slijedu.

Mogućnost serijskog sučelja velike brzine

Namjenski blokovi serijskog sučelja podržavaju komunikacijske kanale velike brzine za prijenos podataka između modula sustava.Ovi se blokovi povezuju s obližnjim I O bankama i pomažu u održavanju stabilnog prijenosa signala u podatkovno intenzivnim dizajnima.

Blokovi strukturirane logike za obradu

Specijalizirani interni blokovi za obradu proširuju logičku strukturu i omogućuju dizajnerima da učinkovitije implementiraju ponovljene digitalne strukture.Ovaj raspored podržava zadatke kao što su rukovanje paketima, sekvenciranje kontrole i paralelne podatkovne operacije.

Programabilna mreža za usmjeravanje

Strukturirana mreža usmjeravanja povezuje logičke ćelije, memorijske blokove i pinove sučelja.Signali mogu putovati kroz mrežu duž više puta, omogućujući dizajnerima da organiziraju digitalne funkcije na načine koji odgovaraju arhitekturi sustava.

Integracija paketa za površinsku montažu

Uređaj se nalazi u paketu s velikom kuglastom mrežom koja podržava gustu integraciju ploče.Ova struktura paketa omogućuje da se mnogi električni priključci rasporede u kompaktnom prostoru za napredne elektroničke sklopove.

LFSC3GA25E-7F900C Tehničke specifikacije

| Svojstvo proizvoda | Vrijednost atributa |

| Proizvođač | Rešetkasti poluvodič |

| Napon - opskrba | 0,95 V ~ 1,26 V |

| Ukupni RAM bitovi | 1966080 |

| Paket uređaja dobavljača | 900-FPBGA (31x31) |

| serije | SC |

| Paket / Kutija | 900-BBGA |

| Paket | Poslužavnik |

| Radna temperatura | 0°C ~ 85°C (TJ) |

| Broj logičkih elemenata/ćelija | 25000 |

| Broj LAB-ova/CLB-ova | 6250 |

| Broj I/O | 378 |

| Vrsta montaže | Površinska montaža |

| Osnovni broj proizvoda | LFSC3GA25 |

| RoHS status | RoHS nije usklađen |

| Razina osjetljivosti na vlagu (MSL) | 3 (168 sati) |

| Status REACH | REACH Bez utjecaja |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Pojednostavljeni blok dijagram LFSC3GA25E-7F900C

Unutarnji raspored LFSC3GA25E-7F900C FPGA koji se temelji na mreži prikazuje raspored programabilne logike, memorijskih blokova, resursa takta i strukture sučelja velike brzine.Programabilne funkcionalne jedinice tvore središnju logičku strukturu gdje se implementiraju konfigurabilni digitalni sklopovi.Distribuirani sysMEM ugrađeni blok RAM odjeljci pružaju unutarnju pohranu podataka i međuspremnik unutar logičkog polja.Programabilne IO ćelije smještene duž rubova uređaja povezuju unutarnju logiku s vanjskim pinovima, pri čemu svaki programabilni IO klaster sadrži više programabilnih IO veza.Četverostruki blokovi SERDES i sučelja podsloja fizičkog kodiranja pojavljuju se u blizini gornjih regija za podršku serijske komunikacije velike brzine.Strukturirani ASIC blokovi s oznakom MACO integrirani su unutar logičke strukture za podršku specijaliziranih obradnih struktura.Resursi za upravljanje taktom označeni kao sysCLOCK analogni PLL-ovi i sysCLOCK DLL-ovi smješteni su na rubove izgleda za generiranje i distribuciju vremenskih signala kroz programabilnu arhitekturu.

Dijagram presjeka LFSC3GA25E-7F900C

Unutarnja struktura logičkog odsječka koji se koristi unutar programabilne funkcijske jedinice LFSC3GA25E-7F900C FPGA.Dva LUT4 bloka izvode kombinacijske logičke operacije koristeći četiri ulazna signala označena s A, B, C i D. Integrirana prijenosna logika podržava aritmetičke operacije povezivanjem prijenosnih ulaznih i prijenosnih izlaznih signala između susjednih odsječaka.Flip flop ili elementi zasuna pohranjuju izlazne podatke iz logičkog stupnja, proizvodeći registrirane izlaze označene Q0 i Q1.Kontrolni ulazi kao što su sat, signali za uključivanje i postavljanje ili resetiranje reguliraju sekvencijalni rad elemenata za pohranu.Veze za usmjeravanje na lijevom i desnom rubu povezuju odsječak s okolnom programibilnom mrežom međusobnog povezivanja, dopuštajući ulaz signala iz resursa za usmjeravanje i vraćanje obrađenih izlaza natrag u strukturu za usmjeravanje.

Primjene LFSC3GA25E-7F900C

Sustavi industrijske kontrole

Programabilni logički resursi omogućuju uređaju upravljanje vremenskim sekvencama, usmjeravanjem signala i zadacima digitalne kontrole u automatiziranoj opremi.Može koordinirati više senzora i aktuatora dok održava stabilnu digitalnu obradu unutar kontrolnog sustava.

Infrastruktura podatkovne komunikacije

Komunikacijska oprema često zahtijeva fleksibilnu digitalnu obradu za rukovanje podacima i kontrolu sučelja.Uređaj može obraditi dolazne tokove podataka, organizirati logiku usmjeravanja i podržavati komunikacijske veze unutar mrežnog hardvera.

Ugrađene računalne platforme

Ugrađeni sustavi koriste programabilnu logiku za upravljanje protokom podataka između procesora, memorije i uređaja sučelja.Uređaj može implementirati prilagođene digitalne staze koje prilagođavaju ponašanje sustava specifičnim zahtjevima aplikacije.

Sustavi za prikupljanje podataka velike brzine

Mjerni sustavi često prikupljaju signale iz više izvora u isto vrijeme.Programabilna logička struktura može organizirati dolazne digitalne signale, uskladiti vrijeme i pripremiti podatke za daljnju obradu ili prijenos.

Hardver za obradu signala

Uređaj može implementirati konfigurabilne aritmetičke i logičke operacije koje podržavaju funkcije obrade signala.Digitalni filtri, upravljačke petlje i zadaci transformacije podataka mogu se implementirati izravno unutar programabilne logičke strukture.

LFSC3GA25E-7F900C Prednosti i nedostaci

Prednosti

• Veliki programabilni logički kapacitet podržava složene digitalne funkcije

• Veliki broj ulaznih i izlaznih priključaka omogućuje fleksibilnu integraciju sustava

• Ugrađeni memorijski blokovi omogućuju unutarnju pohranu podataka i međuspremnik

• Rekonfigurabilna logička struktura omogućuje ažuriranje hardverskih funkcija kroz promjene dizajna

• Više IO banaka omogućuje različite standarde signala unutar jednog uređaja

Nedostaci

• Proces dizajna zahtijeva specijalizirane razvojne alate i konfiguracijske tijekove

• Složenost uređaja može povećati vrijeme dizajna sustava tijekom razvoja

• Velika veličina paketa zahtijeva pažljiv raspored tiskanih ploča

• Upravljanje napajanjem mora se uzeti u obzir kada je mnogo logičkih resursa aktivno

LFSC3GA25E-7F900C Alternative

| Broj dijela | Proizvođač | Ključne značajke | Slučaj/napomene |

| LFSC3GA25E-7FFN1020C | Lattice Semiconductor Corporation | FPGA uređaj iz SC obitelji koji nudi oko 25.000 logičkih elemenata, ugrađene memorijske resurse i velik broj programabilnih I/O pinova.Koristi BGA paket finog koraka koji podržava guste rasporede krugova i složene digitalne dizajne. | Koristi se u ugrađenim kontrolnim sustavima, komunikacijskim sučeljima i industrijskoj elektronici gdje je potreban programabilni hardver i visoka I/O povezanost. |

| LFSC3GA25E-7FFA1020C | Lattice Semiconductor Corporation | Programabilni FPGA sa sličnim logičkim resursima u seriji LFSC3GA25E.Omogućuje konfigurabilne logičke blokove, ugrađenu memoriju i fleksibilno digitalno usmjeravanje koje dizajnerima omogućuje implementaciju prilagođenih digitalnih sklopova. | Prikladno za digitalnu obradu signala, premošćivanje sučelja i programabilnu kontrolu hardvera u ugrađenoj elektronici i komunikacijskim sustavima. |

| LFSC3GA25E-6FN900C | Lattice Semiconductor Corporation | FPGA uređaj s oko 25K logičkih elemenata i integriranih memorijskih blokova dizajniran za programabilni digitalni hardver.Paket pruža mnoge I/O veze koje podržavaju složenu integraciju sustava. | Često se koristi u industrijskim sustavima upravljanja, ugrađenim računalnim platformama i mrežnoj opremi koja zahtijeva fleksibilnu konfiguraciju hardvera. |

O rešetkastom poluvodiču

Lattice Semiconductor je poluvodička tvrtka osnovana 1983. godine sa sjedištem u Hillsboro Oregonu u Sjedinjenim Državama.Tvrtka razvija programabilne logičke uređaje i srodne tehnologije koje se koriste u računalstvu, komunikacijama, industrijskim sustavima i potrošačkoj elektronici.Linije proizvoda uključuju programibilne polja vrata, programabilne logičke uređaje i rješenja za sučelja dizajnirana za podršku dizajnu fleksibilnog digitalnog sustava.Rešetkasti uređaji naširoko se koriste u ugrađenim sustavima gdje programabilne hardverske funkcije pomažu u upravljanju obradom podataka, kontrolnom logikom i usmjeravanjem signala unutar kompaktnih elektroničkih platformi.

Zaključak

LFSC3GA25E-7F900C FPGA kombinira programabilnu logiku, ugrađenu memoriju i fleksibilne ulazno izlazne veze unutar jednog uređaja.Razumijevanjem njegove arhitekture možete vidjeti kako su organizirane digitalne logičke funkcije i kako signali putuju programibilnom strukturom.Značajke kao što su konfigurabilni logički elementi, mreže za usmjeravanje i blokovi za upravljanje satom omogućuju uređaju da podržava mnoge dizajne sustava.Njegova struktura ga čini prikladnim za obradu podataka, upravljačku logiku i komunikacijski hardver.Kada istražite dijagrame i specifikacije, dobivate jasniju sliku o tome kako programabilni hardver podržava prilagodljive elektroničke sustave.

Podatkovna tablica PDF

LFSC3GA25E-7F900C podatkovna tablica:

All Dev Pkg Mark Chg 12/Nov/2018.pdf

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

Često postavljana pitanja [FAQ]

1. Koja je vrsta uređaja LFSC3GA25E-7F900C?

LFSC3GA25E-7F900C je terenski programabilni niz vrata ili FPGA koji omogućuje konfiguraciju digitalnih logičkih sklopova putem hardvera programiranje.Sadrži programabilne logičke blokove, resurse za usmjeravanje, i memorijskih elemenata unutar jednog čipa.

2. Što su logički elementi u LFSC3GA25E-7F900C FPGA?

Logički elementi su male programabilne jedinice unutar FPGA koje obavljanje digitalnih operacija kao što su logičke usporedbe, aritmetika zadaci i obrada signala.Tisuće ovih elemenata rade zajedno za stvaranje prilagođenih hardverskih funkcija.

3. Kako I O banke rade u ovom FPGA?

Ulazne izlazne banke grupiraju skupove pinova koji dijele snagu i referencu naponi.Svaka banka može podržati različite električne standarde, koji omogućuje povezivanje signala s više sučelja na isti uređaj.

4. Koja je svrha ugrađene memorije u uređaj?

Ugrađeni memorijski blokovi pohranjuju podatke unutar FPGA tako da logički sklopovi mogu brzo pristupiti informacijama.Ovi se blokovi koriste za međuspremnik podatke, privremenu pohranu i zadatke obrade signala.

5. Gdje se LFSC3GA25E-7F900C obično koristi?

Ovaj FPGA se obično koristi u komunikacijskim sustavima, industrijskim upravljački hardver, oprema za digitalnu obradu signala i ugrađeni elektroničke platforme gdje je potrebna programabilna digitalna logika.

Što EPF8282AVTC100-4 FPGA radi u digitalnim sustavima

na 2026/03/10

Što je H7 baterija?Veličina, značajke i upotreba vozila

na 2026/03/10

Popularni postovi

-

Složeni računali s uputama: Kako su promijenili računanje?

na 8000/04/17 147711

-

USB-C pinout i značajke

na 2000/04/17 111675

-

Korištenje Xilinx Unified simulacijski primitivi: sveobuhvatni vodič za dizajn i simulaciju FPGA

na 1600/04/17 111314

-

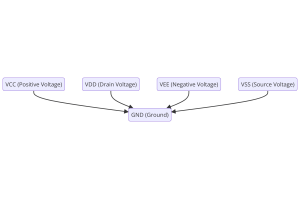

Naponi napajanja u elektronici: Značenje VCC, VDD, VEE, VSS i GND

na 0400/04/17 83582

-

RJ45 Vodič za priključak: pinout, ožičenje, vrste kabela i upotreba

na 1970/01/1 79227

-

Krajnji vodič za kodove u boji žice u modernim električnim sustavima

Način na koji naši električni sustavi koriste boje nisu samo za izgled.Svaka boja žice sada označava određenu funkciju, što olakšava prepoznavanje i ispravno obradu električnih komponenti tijekom u...na 1970/01/1 66752

-

Kvaliteta (q) Faktor: jednadžbe i aplikacije

Faktor kvalitete, ili 'q', važan je prilikom provjere koliko dobro induktori i rezonatori rade u elektroničkim sustavima koji koriste radio frekvencije (RF).'Q' mjeri koliko dobro krug minimizira g...na 1970/01/1 62927

-

Vodič za čišćenje ventila: Funkcija, simptomi, testiranje i zamjena za optimalne performanse motora

Ventil za čišćenje ključni je dio sustava automobila koji pomaže u održavanju zraka čistim upravljanjem parima goriva prije nego što mogu pobjeći u atmosferu.To ne samo da pomaže okolišu smanjenjem...na 1970/01/1 62800

-

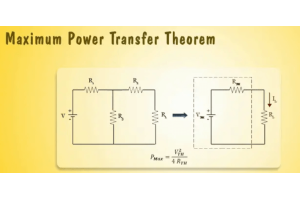

Postizanje vršnih performansi s maksimalnim teoremom prijenosa snage

Teorem maksimalnog prijenosa napajanja objašnjava kako energija iz izvora, poput baterije ili generatora, teče do povezanog opterećenja.Pokazuje točan uvjet u kojem opterećenje prima najviše snage....na 1970/01/1 54020

-

Specifikacije i kompatibilnost A23

A23 baterija je mala baterija u obliku cilindra s visokim naponom.Također se naziva 23A, 23AE ili MN21, radi na 12 volti i mnogo više od AA ili AAA baterija.Njegov poseban dizajn čini ga s...na 1970/01/1 51950