XC2S50-5TQG144I FPGA: Značajke, specifikacije, aplikacije i vodič za programiranje

XC2S50-5TQG144I je fleksibilan i moćan FPGA (terenska programabilna vrata) iz Spartan-II obitelji AMD Xilinx.Dizajniran je za digitalne projekte kojima je potrebna prilagodba, brzina i pouzdanost.Ovaj vodič objašnjava značajke, specifikacije, proces programiranja i upotrebu ovog FPGA kako bi vam pomogao da shvatite kako to maksimalno iskoristiti.Katalog

XC2S50-5TQG144I pregled

A XC2S50-5TQG144I je Spartan-II FPGA iz AMD Xilinx, dizajniran za digitalne projekte koji trebaju fleksibilnost i performanse.Ima 50.000 kapija sustava i 1.728 logičkih ćelija, što mu omogućava rukovanje složenim zadacima.Čip uključuje 384 konfigurabilnih logičkih blokova (CLB) i 32.768 RAM bita, što mu daje dobru memoriju i obradu snage.S 92 ulazne/izlazne (I/O) igle, lako se može povezati s drugim komponentama.Dolazi u 144-pinskom tankom quad ravnom paketu (TQFP), koji je kompaktan i jednostavan za upotrebu.FPGA radi na 2,5 V (sa sigurnim rasponom od 2,375 V do 2,625 V) i dobro funkcionira u temperaturama između -40 ° C i +100 ° C.Ova Spartan-II FPGA izrađena je s tehnologijom 0,18-mikrona, što ga čini učinkovitim i pouzdanim.Programiran je, što znači da možete ažurirati njegove funkcije po potrebi.

Za ekonomično, visoko performanse rješenje, optimalan izbor je postavljanje rasutih narudžbi, osiguravajući vrhunsku kvalitetu.

XC2S50-5TQG144I CAD modeli

XC2S50-5TQG144I simbol

XC2S50-5TQG144I

XC2S50-5TQG144I 3D model

XC2S50-5TQG144I značajke

• Kapije sustava: XC2S50-5TQG144i FPGA nudi oko 50 000 kapije sustava.To mu omogućuje podržavanje složenih digitalnih dizajna i aplikacija koje zahtijevaju značajnu količinu mogućnosti logičke obrade.

• Logičke stanice: Ovaj uređaj uključuje 1.728 logičkih ćelija koje olakšavaju implementaciju zamršenih logičkih konfiguracija i stvaranje različitih digitalnih funkcionalnosti unutar FPGA.

• Konfigurirajući logički blokovi (CLB): Sadrži 384 konfigurabilne logičke blokove (CLBS), koji pružaju temelj za logiku FPGA.Ovi se blokovi mogu programirati i rekonfigurirati kako bi ispunili određene zahtjeve dizajna, poboljšavajući ukupnu svestranost uređaja.

• OVAN: FPGA je opremljen s 32.768 bita unutarnjeg RAM -a, nudeći učinkovite mogućnosti pohrane i pretraživanja podataka za zadatke koji uključuju manipulaciju podataka i privremenu pohranu podataka.

• I/O igle: S 92 I/O igle, XC2S50-5TQG144i osigurava dovoljno vanjskog povezivanja, omogućujući mu da se sučelja s drugim uređajima i komponentama u sustavu za sveobuhvatnu integraciju sustava.

• Radni napon: Uređaj djeluje s nominalnim naponom od 2,5 V, s prihvatljivim rasponom od 2,375V do 2,625V.Ovaj raspon napona pomaže osigurati stabilan rad i pouzdane performanse u različitim električnim uvjetima.

• Temperaturni raspon: XC2S50-5TQG144i dizajniran je za učinkovito djelovanje u širokom temperaturnom rasponu, od -40 ° C do +100 ° C, što ga čini prikladnim za implementaciju u okruženjima s izazovnim toplinskim uvjetima.

XC2S50-5TQG144I Blok dijagram

Dijagram pokazuje kako se signali kreću i izlazi iz XC2S50-5TQG144I FPGA.Objašnjava kako čip obrađuje ulazne i izlazne signale za komunikaciju s drugim komponentama.Na izlazna strana , Signali dolaze iz FPGA i prolaze kroz jedinice za pohranu nazvane flip-flops.Ovi flop-flops drže podatke i osiguravaju da se signali mijenjaju u pravo vrijeme.Signali tada prolaze kroz programibilni izlazni međuspremnik, koji prilagođava koliko je jak signal i kontrolira koliko se brzo mijenja.Postoji i prekidač (OE kontrola) koji odlučuje treba li izlaz biti aktivan ili ostati isključen.Zaštitni krug sprječava oštećenja od statičkog elektrika prije nego što signal dosegne I/O igle, koji se povezuju s drugim uređajima.Na ulazna strana, signali izvana ulaze kroz programibilni ulazni međuspremnik, koji ih obrađuje prije nego što ih pošaljete unutar FPGA.Programirajuća jedinica kašnjenja pomaže u podešavanju vremena signala tako da sve ostane u sinkronizaciji.FPGA također može koristiti unutarnji referentni napon (VREF) kako bi odgovarao različitim razinama napona, što olakšava rad s različitim vrstama krugova.Neki I/O pinovi dijele ovu referencu napona kako bi se signale držali stabilnim.Ovaj dizajn pomaže FPGA učinkovito upravljati signalima, osiguravajući pravilno vrijeme, zaštitu i kompatibilnost s različitim elektroničkim komponentama.

XC2S50-5TQG144I Specifikacije

|

Tip |

Parametar |

|

Proizvođač |

AMD Xilinx |

|

Niz |

Spartan®-II |

|

Pakiranje |

Pladanj |

|

Status dijela |

Zastario |

|

Broj laboratorija/CLB -a |

384 |

|

Broj logičkih elemenata/stanica |

1728 |

|

Ukupni RAM komadići |

32.768 |

|

Broj I/O |

92 |

|

Broj vrata |

50.000 |

|

Napon - napad |

2.375V ~ 2.625V |

|

Montažni tip |

Površinski nosač |

|

Radna temperatura |

-40 ° C ~ 100 ° C (TJ) |

|

Paket / slučaj |

144-lqfp |

|

Paket uređaja dobavljača |

144-TQFP (20x20) |

|

Broj osnovnog proizvoda |

XC2S50 |

XC2S50-5TQG144I aplikacije

Ugrađeni sustavi

U ugrađenim sustavima, XC2S50-5TQG144I pruža potrebnu logiku za aplikacije temeljene na mikrokontrolerima.Opsežno se koristi u automobilskoj elektronici, prijenosnim uređajima i malim robotikama za poboljšanje funkcionalnosti i reaktivnosti.

Obrada signala

FPGA se ističe u zadacima obrade signala, gdje je potrebna njegova sposobnost izvođenja paralelne obrade.Idealan je za audio i video obradu, telekomunikacije i analizu podataka, pružajući konjsku snagu za rukovanje složenim algoritmima i brzim tokovima podataka.

Industrijski upravljački sustavi

Sustavi za industrijsku kontrolu imaju koristi od robusnosti i programabilnosti ovog FPGA, što ga čini prikladnim za aplikacije kao što su kontrola procesa, automatizacija strojeva i nadzor sustava.Njegova pouzdanost osigurava dosljedne performanse u okruženjima koja zahtijevaju preciznost i operativnu stabilnost.

Komunikacijski sustavi

U komunikacijskim sustavima XC2S50-5TQG144i pomaže u upravljanju prijenosom i prijemom podataka, podržavajući aktivnosti kao što su modulacija signala i demodulacija, pretvorba protokola i usmjeravanje mreže.Njegova prilagodljivost ključna je u razvoju telekomunikacijske infrastrukture i novih bežičnih tehnologija.

Prototipizacija i razvoj

FPGA se također intenzivno koristi za prototipiranje digitalnih krugova.Mnogi ga koriste za testiranje i pročišćavanje svojih ideja prije konačne proizvodnje, posebno u složenim ASIC i prilagođenim projektima dizajna čipova.Ova sposobnost smanjuje vrijeme i troškove razvoja, ubrzavajući put od koncepta na tržište.

XC2S50-5TQG144I slični dijelovi

XC2S50-5TQG144I Prednosti

Ekonomičnost

XC2S50-5TQG144I ističe se po svojoj pristupačnosti, pružajući više značajki po dolaru od mnogih konkurentskih FPGA-ova.Ova isplativost postiže se naprednom procesnom tehnologijom i učinkovitom arhitekturom, što omogućava širu implementaciju na tržištima osjetljivim na troškove.

I/O i pakiranje visokih performansi

Ovaj FPGA podržava širok raspon I/O standarda i dostupan je u različitim ekonomičnim mogućnostima pakiranja.Ove značajke osiguravaju da se uređaj može integrirati u više aplikacija bez žrtvovanja performansi, što ga čini idealnim za tržišta vrhunskih i volumena, gdje su svestranost sučelja i fizička ograničenja faktori.

Značajke na razini sustava

Opremljen naprednim značajkama upravljanja memorijom kao što su distribuirani RAM i konfigurirajući blok RAM-a, XC2S50-5TQG144i poboljšava učinkovitost rukovanja podacima.Ove značajke olakšavaju složene zadatke za pohranu i obradu podataka, povećavajući ukupnu performanse i skalabilnost sustava.

Reprogramiranje

Reprogramiranost XC2S50-5TQG144i omogućava neograničene modifikacije svoje konfiguracije, što je korisno tijekom faze razvoja.Ova fleksibilnost omogućuje usavršavanje dizajna kroz iterativna ažuriranja bez dodatnih troškova hardvera, poticanje inovacija i smanjenje vremena na konačni proizvod.

XC2S50-5TQG144i Koraci programiranja

Programiranje XC2S50-5TQG144I FPGA iz serije Spartan-II AMD Xilinx uključuje strukturirani niz koraka dizajniranih za učinkovito prevođenje digitalnog dizajna u funkcionalnu FPGA konfiguraciju.Evo integriranog i detaljnog vodiča koji će vam pomoći kroz proces programiranja:

1. Unos dizajna

Započnite s fazom unosa dizajna, gdje stvarate svoju digitalnu logiku pomoću jezika hardverskog opisa (HDL), poput VHDL ili Verilog.Ovaj početni korak uključuje detalje o funkcionalnosti i logici koju želite implementirati u FPGA.Potrebno je da vaš dizajn bude precizan i točno predstavlja predviđene operacije kako bi se osigurala uspješna sinteza i implementacija.

2. Sinteza

U koraku sinteze koristite alat za sintezu za pretvorbu HDL koda u netlist.Netlist je slom vašeg dizajna u format koji uključuje različite međusobno povezane logičke elemente kao što su vrata i flip-flops.Ovaj postupak prevodi vaš teorijski dizajn u praktični nacrt koji FPGA može razumjeti i implementirati.

3. Provedba

Provedba uključuje nekoliko pod-koraka: mapiranje, postavljanje i usmjeravanje.Mapiranje dodjeljuje elemente vašeg netLista određenim logičkim blokovima unutar FPGA.Postavljanje određuje fizičke lokacije ovih blokova na FPGA čip za optimiziranje performansi i korištenja resursa.Usmjeravanje povezuje ove blokove putem FPGA -ovih programabilnih resursa za međusobno povezivanje.Ova faza osigurava da dizajn ispunjava sva fizička i performansi ograničenja.

4. Definicija ograničenja

Tijekom procesa dizajniranja potrebno je definiranje ograničenja.Ograničenje Vodi alati za implementaciju određivanjem zahtjeva kao što su vrijeme (koliko brzo FPGA treba raditi) i prisluškivanja (koje će se igle na FPGA povezati s različitim dijelovima vašeg hardvera).Oni su artikulirani u datoteci korisničkih ograničenja (UCF), koja pomaže u finom podešavanju dizajna kako bi se zadovoljile određene operativne standarde.

5. Generacija bitstreama

Jednom kada vaš dizajn uspješno prođe kroz fazu implementacije, sljedeći korak je generiranje datoteke BitStream.Ova datoteka sadrži sve podatke o konfiguraciji potrebnim FPGA za izvršavanje dizajna.Bitstream je konačni izlaz procesa programiranja, koji predstavlja cjelovito, programirano stanje FPGA.

6. Programiranje uređaja

Posljednji korak je učitavanje bitstreama u XC2S50-5TQG144i FPGA, što se može učiniti pomoću različitih načina konfiguracije, ovisno o vašem postavljanju.U Glavni serijski način, FPGA autonomno čita konfiguracijske podatke s priložene serijske maturante (programabilna memorija samo za čitanje). Serijski način robova Omogućuje vanjskom glavnom uređaju, poput mikrokontrolera, da se serijski napaja podaci o konfiguraciji FPGA. Robovi paralelni način Omogućuje programiranje velike brzine davanjem konfiguracijskih podataka paralelno s vanjskog glavnog uređaja.Na kraju, Način graničnog skeniranja (JTAG) Koristi JTAG sučelje i za programiranje i testiranje, što ga čini korisnim tijekom razvoja za iterativno uklanjanje pogrešaka i provjere.

XC2S50-5TQG144I Dimenzije pakiranja

A XC2S50-5TQG144I Je li terenska programabilna niz vrata (FPGA) iz Xilinxove obitelji Spartan-II, smještena u a 144-pinski tanki quad ravni paket (TQFP) paket.Ovaj paket mjeri 20 mm x 20 mm.

XC2S50-5TQG144I Proizvođač

XC2S50-5TQG144I je FPGA iz obitelji Spartan-II, koju je proizvela AMD Xilinx.Xilinx, sada dio AMD, vodeća je poluvodička tvrtka specijalizirana za FPGAS, adaptivne SOC -ove i druge programabilne logičke uređaje.XC2S50-5TQG144I izvorno je razvijen u seriji Xilinx Spartan-II, nudeći 50.000 kapije sustava i 1.728 logičkih ćelija, dizajniranih za visoke performanse, a opet isplative aplikacije.S Xilinxovom akvizicijom od strane AMD-a, tvrtka nastavlja podržavati naslijeđene proizvode poput Spartan-II serije dok napreduje novijim FPGA arhitekturama.Međutim, XC2S50-5TQG144I je FPGA starije generacije i može se suočiti s eventualnom zastarjelom jer se AMD Xilinx premješta na naprednije FPGA obitelji.

Zaključak

XC2S50-5TQG144I FPGA je isplativ i reprogramirajući čip koji nudi izvrsne performanse i fleksibilnost.Široko se koristi u ugrađenim sustavima, industrijskim strojevima i komunikacijskim mrežama zbog svoje velike prerade i snažnih mogućnosti povezivanja.Sa svojom sposobnošću da se programira i ažurira, ovaj FPGA pomaže testirati i razviti nove ideje prije konačne proizvodnje.Iako su dostupni noviji FPGA, ovaj model ostaje solidan izbor za projekte koji trebaju pouzdano i pristupačno FPGA rješenje.Ovaj vodič pruža jasan i jednostavan pregled značajki, upotrebe i programiranja FPGA -e, što ga čini dragocjenim resursom za sve.

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

Često postavljana pitanja [FAQ]

1. Mogu li koristiti XC2S50-5TQG144I za velike brzine?

XC2S50-5TQG144i podržava brzinu do 200 MHz, što ga čini prikladnim za većinu ugrađenih i industrijskih primjena.Međutim, ako vaš projekt zahtijeva sučelja velike brzine poput PCIE ili DDR memorije, možda će vam trebati naprednija FPGA poput Spartan-6 ili Artix-7 serije.

2. Kako se XC2S50-5TQG144I uspoređuje s novijim Spartan-3 ili Spartan-6 FPGAS?

Dok noviji FPGA-ovi poput Spartan-3 ili Spartan-6 nude poboljšane performanse, veću logičku gustoću i dodatne značajke, XC2S50-5TQG144i ostaje preferirani izbor za projekte osjetljive na troškove s umjerenom složenošću.Ako vam je potrebna naslijeđena kompatibilnost ili stabilan opskrbni lanac, XC2S50-5TQG144i je sjajna opcija.

3. Koji su programski alati kompatibilni s XC2S50-5TQG144i FPGA?

XC2S50-5TQG144I je programiran pomoću Xilinx ISE (integrirano softversko okruženje).Dok noviji Xilinx alati poput Vivado ne podržavaju Spartan-II obitelj, ISE pruža sve potrebne funkcionalnosti dizajna, sinteze i programiranja za ovaj FPGA.

4. Mogu li premjestiti postojeći Spartan-II dizajn na noviji FPGA?

Da, ali to zahtijeva izmjene.Novije obitelji Spartan-3 i Spartan-6 koriste različite arhitekture, razine napona i metode konfiguracije.Ako razmišljate o migraciji, možemo vam pomoći u odabiru odgovarajućih alternativa i minimiziranju promjena dizajna.

5. podržava li XC2S50-5TQG144I programiranje JTAG-a?

O: Da, FPGA podržava programiranje graničnog skeniranja JTAG (IEEE 1149.1), što omogućava jednostavno uklanjanje pogrešaka i konfiguracije pomoću standardnog JTAG sučelja.Ovo je korisno i za početno programiranje i za rekonfiguraciju bez vanjske memorije.

XC4013XL-3PQ240C FPGA: alternative, specifikacije, aplikacije i podatkovni list

na 2025/03/18

RF pojačala napajanja: kako rade, koja je vrsta učinkovitija

na 2025/03/18

Popularni postovi

-

Složeni računali s uputama: Kako su promijenili računanje?

na 8000/04/17 147713

-

USB-C pinout i značajke

na 2000/04/17 111748

-

Korištenje Xilinx Unified simulacijski primitivi: sveobuhvatni vodič za dizajn i simulaciju FPGA

na 1600/04/17 111324

-

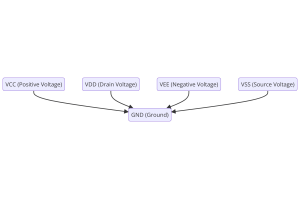

Naponi napajanja u elektronici: Značenje VCC, VDD, VEE, VSS i GND

na 0400/04/17 83638

-

RJ45 Vodič za priključak: pinout, ožičenje, vrste kabela i upotreba

na 1970/01/1 79295

-

Krajnji vodič za kodove u boji žice u modernim električnim sustavima

Način na koji naši električni sustavi koriste boje nisu samo za izgled.Svaka boja žice sada označava određenu funkciju, što olakšava prepoznavanje i ispravno obradu električnih komponenti tijekom u...na 1970/01/1 66791

-

Kvaliteta (q) Faktor: jednadžbe i aplikacije

Faktor kvalitete, ili 'q', važan je prilikom provjere koliko dobro induktori i rezonatori rade u elektroničkim sustavima koji koriste radio frekvencije (RF).'Q' mjeri koliko dobro krug minimizira g...na 1970/01/1 62953

-

Vodič za čišćenje ventila: Funkcija, simptomi, testiranje i zamjena za optimalne performanse motora

Ventil za čišćenje ključni je dio sustava automobila koji pomaže u održavanju zraka čistim upravljanjem parima goriva prije nego što mogu pobjeći u atmosferu.To ne samo da pomaže okolišu smanjenjem...na 1970/01/1 62842

-

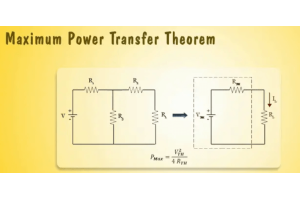

Postizanje vršnih performansi s maksimalnim teoremom prijenosa snage

Teorem maksimalnog prijenosa napajanja objašnjava kako energija iz izvora, poput baterije ili generatora, teče do povezanog opterećenja.Pokazuje točan uvjet u kojem opterećenje prima najviše snage....na 1970/01/1 54038

-

Specifikacije i kompatibilnost A23

A23 baterija je mala baterija u obliku cilindra s visokim naponom.Također se naziva 23A, 23AE ili MN21, radi na 12 volti i mnogo više od AA ili AAA baterija.Njegov poseban dizajn čini ga s...na 1970/01/1 52012