Inovativni vodič za JK Flip-flops: Analiza tablica, mehanizama i strateških primjena istine i strateških primjena

Ovaj članak istražuje arhitekturu, rad i raznolike primjene JK Flip-Flop-a, počevši od svoje osnovne strukture i odnosa ulaznih izlaza, kroz detaljnu operativnu mehaniku, do svojih strateških implementacija u složenim digitalnim sustavima.Diskurs se proširuje na razlikovanje varijanti koje su progutale rubom i na razini, analizirajući njihove komunalne usluge u sinkronom i asinhronom okruženju.Katalog

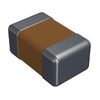

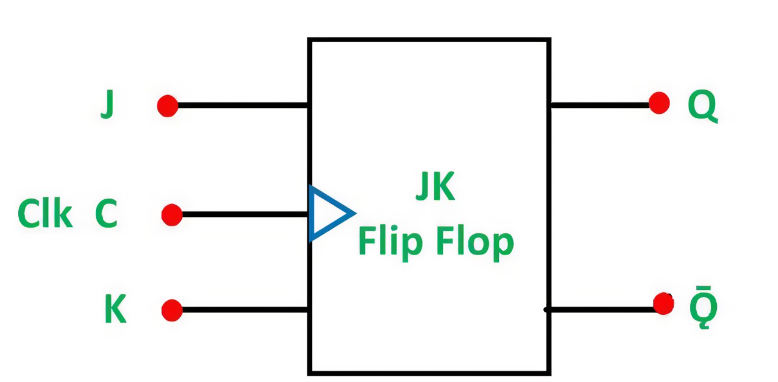

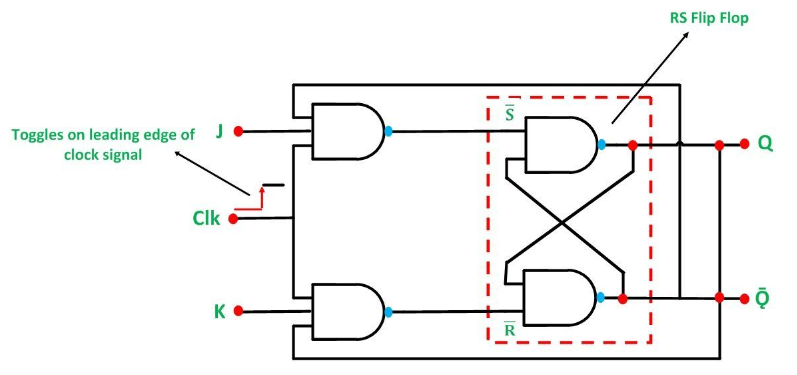

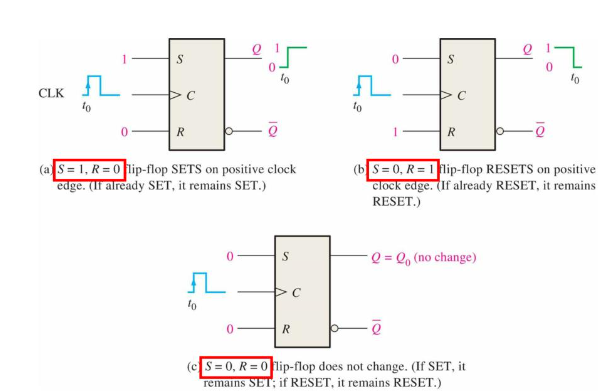

Slika 1: JK Flip-Flop

Osnove JK Flip-Flop

JK Flip-Flop osnovna je komponenta u digitalnoj elektronici, dizajnirana za pohranjivanje jednog zalogaja informacija.Izrađuje se na jednostavnijem SR flip-flopu dodavanjem povratnih informacija, što pomaže u sprječavanju pogrešaka poznatih kao "uvjeti rase", gdje izlaz postaje nestabilan.

Ovaj flip-flop ima dva glavna ulaza, j (set) i k (resetiranje) i dva izlaza: q i njegov komplement, q '.Ovi izlazi kontinuirano odražavaju trenutno stanje i njegovo suprotno, omogućujući da se krug prilagodi i reagira na ulazne promjene u stvarnom vremenu.

JK Flip-Flop djeluje na specifične načine na temelju ulaznih vrijednosti:

• Kad su i J i K 0: Flip-flop drži svoje trenutno stanje.Ne događaju se promjene.

• Kad su i J i K 1: Flip-flop prebacuje svoje stanje.Ako je q 0, postaje 1;Ako je Q 1, prebacuje se na 0. Ova je preklopna akcija ključna značajka koja razlikuje JK Flip-Flop od jednostavnijih dizajna.

• Kad je j 1, a K je 0: Flip-flop postavlja svoje stanje, čineći q jednakom 1.

• Kad je j 0, a K je 1: Flip-flop se resetira, čineći q jednakim 0.

Rad JK Flip-Flop

JK Flip-Flop igra ključnu ulogu u digitalnim krugovima upravljanjem memorijom i vremenom kroz koordinirani odgovor na ulazne signale i impulse sata.Njegov rad uvelike ovisi o vremenu ulaza J i K u odnosu na signal sata, što određuje kako se izlazna stanja (Q i Q̅) mijenjaju.Ova sinkronizacija osigurava da se flip-flop ponaša predvidljivo u različitim aplikacijama kruga.Flip-flop se oslanja na NAND ili NOR Gates za upravljanje tim promjenama stanja.

Držeći trenutno stanje- Kad su i J i K ulazi niski (0), flip-flop zadržava svoje trenutno stanje.Logička vrata učinkovito "zaključavaju" izlaze, osiguravajući održavanje prethodnog stanja (bilo visoko ili niskog).Ova je funkcija zadržavanja ozbiljna u aplikacijama u kojima podaci moraju ostati stabilni dok određena promjena nije obavezna.

Postavljanje izlaza visoko (postavljeno stanje) -Kad se pojavi impuls sata i J je visok (1), dok k ostaje nizak (0), logička vrata se prilagođavaju za postavljanje flip-flopa.To pokreće izlaz Q u visoko stanje (1).Ovo je korisno u situacijama kada krug mora pokrenuti visoki izlaz, na primjer, aktiviranje uređaja ili pohranu "1" u memoriju.

Čišćenje izlaza nisko (resetiranje stanje) - Ako je j nizak (0), a k je visok (1) u vrijeme pulsa sata, prelazni flip-flop u stanje resetiranja, prisiljavajući q da pođe nisko (0).Ova radnja resetiranja često se koristi u krugovima kojima je potrebno zadano ili očišćeno stanje nakon završetka operacije, poput uklanjanja podataka iz memorije.

Prebacivanje izlaza - Jedinstvena značajka Flip-Flopa pojavljuje se kada su i J i K visoki (1).Kad stigne impuls sata, okretni flop se prebacuje, prebacujući izlaz iz svog trenutnog stanja u suprotno.Ako je Q visok, postaje nizak, a ako je q nizak, postaje visok.Ova preklopna funkcija uporno je na aplikacijama poput brojača ili uređaja koji se moraju automatski izmjenjivati između stanja.

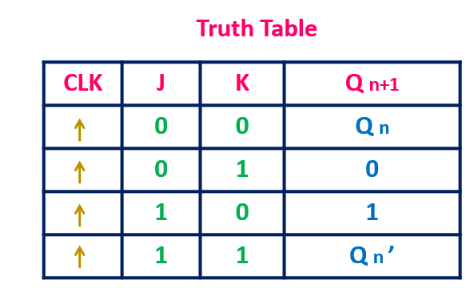

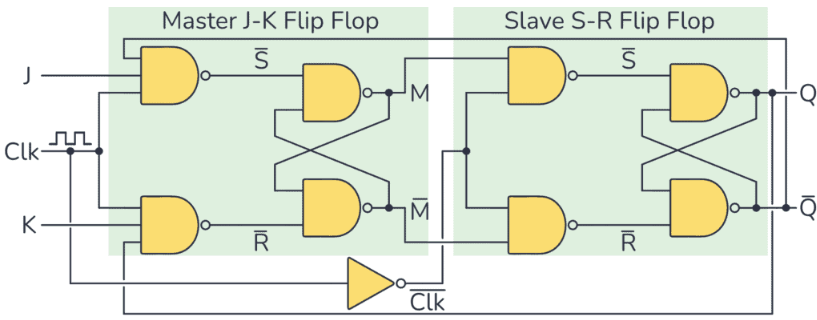

Slika 2: Tablica istine JK Flip-Flop

JK Flip-flop Tablica Tablica analiza

Tablica istine JK Flip-Flop ključni je alat za vizualizaciju kako reagira na različite ulazne signale u sinkronizaciji s impulsima sata.Ova tablica pomaže i u dizajniranju i u rješavanju problema s digitalnim krugovima pokazujući kako se izlazi Flip-Flopa mijenjaju na temelju različitih ulaznih uvjeta.

• i j i k niski (j = 0, k = 0): Kad su oba ulaza 0, flip-flop ima svoje trenutno stanje.Bilo da je Q visok ili nizak, ostaje nepromijenjen.To je zapaženo za krugove u kojima se traže stabilno zadržavanje podataka, poput elemenata u memoriji, gdje je očuvanje trenutnog stanja prikladno dok se ne pokrene određena promjena.

• j visok, k niska (j = 1, k = 0): Kad je j 1, a K je 0, flip-flop postavlja izlaz Q na visok (1).Ovaj uvjet postavke koristan je u aplikacijama koje zahtijevaju precizan okidač za aktiviranje operacije, poput uključivanja uređaja ili pokretanja niza u logičkom krugu.

• j niska, k visoka (j = 0, k = 1): S j na 0 i k na 1, flip-flop se resetira, čineći q nisku (0).Ova je funkcija resetiranja ozbiljna u sustavima koji se moraju vratiti u zadano stanje, poput čišćenja podataka ili inicijalizacije postupka.

• i J i K visoki (j = 1, k = 1): Kad su oba ulaza visoka, flip-flop prebacuje svoje stanje.Ako je q visok, postaje nizak, a ako je q nizak, prelazi na visoko.Ovo prebacivanje ponašanja značajno je za uređaje koji se moraju izmjenjivati između država, poput frekvencijskih razdjelnika ili šaltera.

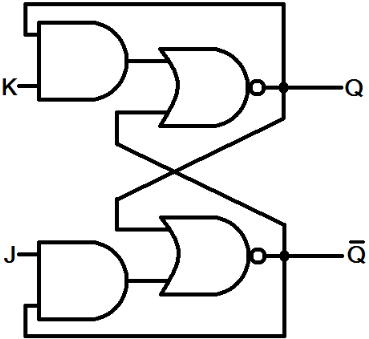

Slika 3: JK zasun

Uvidi u JK zasun i koristi

JK zasun djeluje slično kao JK Flip-Flop, ali bez potrebe za signalom sata.Umjesto da čeka rub sata, zasun JK kontinuirano reagira na ulazne promjene, čineći ga "razinom osjetljivim".To znači da je sve dok su ulazi (j i k) stabilni, izlaz će se promijeniti u stvarnom vremenu, nudeći neposredne povratne informacije na temelju ulaznih uvjeta.

Za razliku od JK-Flip-Flop-a, koji je odiše rubom, koji ažurira svoj izlaz samo kad se signal sata mijenja (od niskog do visokih ili obrnuto), JK zasun prilagođava svoj izlaz odmah kako se ulazi pomaknu.Ova stalna reaktivnost u stvarnom vremenu vrijedna je u scenarijima u kojima se želi neposredna radnja bez kašnjenja uzrokovanog sinkronizacijom sata.

Filteri za buku: U digitalnim krugovima koji trebaju brzo filtrirati neželjeni šum, utjecaj je trenutna reakcija JK zasuka na ulazne promjene.Budući da ne čeka impuls sata, može prilagoditi izlaz čim se otkrije buka, sprječavajući kašnjenje u korekciji signala.

Jednostavni elementi memorije: JK zasun može poslužiti kao osnovna memorijska jedinica u sustavima koji nisu potrebni složeni, takto kontrolu.Budući da zasun održava izlaz stabilnim sve dok se ulazi ne mijenjaju, on učinkovito drži trenutno stanje, što je korisno za krugove koji trebaju zadržati informacije bez režijskih operacija.

Slika 4: Analiza dijagrama vremena za JK Flip-Flop

Analizirajući vremenski dijagram JK Flip-flops

Vremenski dijagram JK Flip-Flop pruža vizualni kvar kako izlaz reagira na različite ulaze, sinkroniziran s prijelazima pulsa sata.Ovaj dijagram prikazuje odnos između signala sata (CLK) i ulaza (j i k) i kako oni zajedno utječu na izlaze (q i q ').Pomaže u preslikavanju ponašanja Flip-Flopa kroz uzastopna stanja, što olakšava razumijevanje njegovog rada.

Prvo, dijagram Izdvaja da se izlazi ažuriraju samo na porastu ili padajućim rubovima pulsa sata.Ova značajka, poznata pod nazivom Edge, dominantna je u operaciji JK Flip-Flopa.Pokazuje da čak i ako se ulazi J i K promijene, izlaz ostaje nepromijenjen dok se ne pojavi rub sata, osiguravajući predvidljivi i stabilni prijelazi.

Zatim, dok dijagram preslikava varijacije ulaza J i K, vizualno pokazuje kako svaka ulazna kombinacija utječe na izlaz. Na primjer, kada su i j i k niski (0), izlaz ima svoje trenutno stanje.Kad je j visok, a k niska, izlaz je postavljen.Ovaj jasni vizualni prikaz pomaže korisnicima da shvate kako Flip-Flop reagira na različite kombinacije unosa u stvarnom vremenu.

Konačno, Dijagram vremena jasno prikazuje prijelaze između različitih izlaznih stanja, bilo da su držanje, postavljanje, resetiranje ili prebacivanje.Svaka promjena stanja vezana je izravno za ulazne uvjete i rub sata, pokazujući uzročno-posljedično odnos koji je žarište za projektiranje i rješavanje problema.

Svestrane primjene JK Flip-flops

JK Flip-flops su temeljne komponente u širokom rasponu digitalnih sustava, poznatih po svojoj fleksibilnosti i pouzdanosti.Njihova sposobnost rukovanja složenim logičkim operacijama čini ih potrebnim u nekoliko ključnih aplikacija, uključujući:

Slika 5: pohrana memorije

JK Flip-flops obično se koriste za pohranjivanje pojedinih bitova podataka, što ih čini temeljnim elementima u memorijskim nizovima i registrima.Svaki flip-flop drži jedan bit, osiguravajući pouzdano pohranjivanje podataka, što je korisno u dizajnu većih memorijskih sustava.

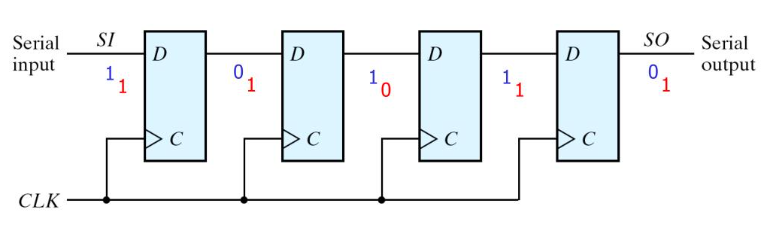

Slika 6: Registri brojača i pomaka

JK flip-flops su dinamični u operacijama sekvenciranja.Oni se široko koriste u šalterima za brojanje događaja ili impulsa i u registrima pomaka za pretvaranje serijskih podataka u paralelne formate.To ih čini korisnima u upravljanju i manipuliranju podataka u različitim fazama procesa, poput komunikacijskih sustava.

Slika 7: Odjel frekvencije

U obradi signala, JK-flops često se koriste za podjelu frekvencije.Prebacivanjem njihovog stanja svakim impulsom sata, oni podijele frekvenciju ulaznog signala, stvarajući sporiji, upravljiviji signal sata.To je zapaženo u aplikacijama poput upravljanja signalima sata, gdje je željena kontrola vremena.

Slika 8: Sinkronizacija

JK Flip-flops pomažu u sinkronizaciji više digitalnih procesa osiguravajući da različiti dijelovi sustava djeluju zajedno na koordiniran način.Osiguravaju da razne komponente ispravno reagiraju na tempirane signale, zadržavajući cijeli sustav u sinkronizaciji.

Slika 9: JK Flip-Flop: Ispunjen rubom i na razini

Različite vrste jk flip-flops

JK Flip-flops dostupni su u dvije glavne vrste: rubova i propuštena na razini, svaki dizajniran za različite operativne zahtjeve.

JK-flip-flops s rubom: Promijenite svoje stanje samo u određenim točkama - kada signal sata prijeđe s niskog u visoki (rastući rub) ili visok do nisko (padajući rub).Ova karakteristika čini ih idealnim za sustave u kojima je precizno vrijeme uporno.Budući da se promjene stanja događaju točno na rubu sata, ovi flip-flops osiguravaju da se sva ažuriranja događaju u sinkronizaciji s pulsom sata.Ovo predvidljivo ponašanje dinamično je u strogo kontroliranim okruženjima kao što su digitalni satovi, registri i većina uzastopnih krugova.Ovdje je vrijeme svake promjene ozbiljno za održavanje stabilnosti sustava i osiguravanje sinkronizacije operacija.

JK-flip-flops s propuštenim na razini: Radite drugačije, reagirajući na ulazni signal sve dok je signal sata na određenoj razini - bilo visok ili nizak.Ne čekaju određeni prijelaz sata.Umjesto toga, sve dok ulaz ispunjava potrebne uvjete, flip-flop će promijeniti stanja.Ovo ponašanje čini da se naleti na razinu flip-flops pogodnije za asinhrone sustave, gdje se ulazi možda neće uskladiti s redovitim impulsom sata.Oni pružaju fleksibilnost u sustavima u kojima su ulazi nepredvidivi ili dolaze u nepravilne intervale, poput određenih zadataka obrade signala ili sustava za praćenje koji moraju odmah reagirati na promjenu ulaza.

Prednosti i nedostaci JK Flip-Flop

JK Flip-flops nudi nekoliko prednosti, ali također dolaze s nekim kompromisima koje je potrebno pažljivo odmjeriti prilikom dizajniranja digitalnih sustava.

|

Profesionalci |

|

|

Svestranost |

JK Flip-flops su vrlo fleksibilni i mogu

koristiti u raznim digitalnim krugovima poput memorije pohrane, šaltera i

upravljački sustavi.Mogu prebaciti, postaviti ili resetirati na temelju različitih unosa

uvjeti, čineći ih prikladnim za širok raspon aplikacija koje

zahtijevaju preciznu kontrolu nad državnim prijelazima. |

|

Mehanizam samo-ispravljanja |

Jedna od izdvojenih značajki JK

flip-flops je njihova ugrađena petlja za povratne informacije, koja pomaže ispraviti logično

navodi dinamički.Ova samokorekcija osigurava da krug ostane

stabilna tijekom rada, čak i kada se ulazi brzo mijenjaju. |

|

Ublažavanje stanja utrke |

Za razliku od jednostavnijih flip-flops-a, jk flip-flops

dizajnirani su tako da spriječe uvjeti utrke - sjedinje u kojima izlaz postaje

nestabilno zbog sukobljenih ulaznih signala.Ova sposobnost održavanja

dosljedan izlaz, čak i pod brzim i uzastopnim ulaznim promjenama, poboljšava

Pouzdanost kruga. |

|

Nedostaci |

|

|

Složeni dizajn |

JK flip-flops su složeniji od

Osnovni flip-flops.Njihov dizajn zahtijeva dodatna logička vrata i unos

nadzor, što krug može otežati dizajniranje i

Rješavanje problema, posebno u sustavima u kojima se preferira jednostavnost. |

|

Kašnjenje širenja |

Unutarnja gatina koristila za upravljanje državom

Prijelazi uvodi kašnjenje u načinu na koji se brzi signali mogu obraditi.U

Aplikacije velike brzine, ovo kašnjenje može utjecati na ukupno vrijeme i usporiti

Izvedba kruga. |

|

Veća potrošnja energije |

Zbog njihove složenosti i potrebe za

Stalno nadgledajte ulazne uvjete, JK flop-flops troši više snage

u usporedbi s jednostavnijim flip-flopsima.U većim sustavima ili osjetljivim na snagu

aplikacije, ova veća potražnja za energijom može postati nedostatak |

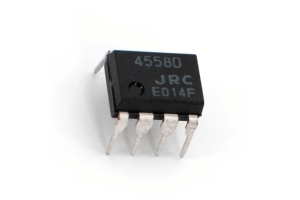

Slika 10: Master-Rove JK Flip-Flop

Dekodiranje majstorskog slave JK Flip-Flop

JK Flip-flop Master-slave dizajniran je za rješavanje uvjeta utrke koje se nalazi u standardnim JK flip-flops koristeći postupak u dva koraka za učinkovitije upravljanje ulazima i izlazima.

Prva faza, nazvana glavna pozornica, bilježi ulazne vrijednosti kada signal sata dosegne određeni rub, bilo porast ili pada.U ovom se trenutku ulazni podaci zaključavaju, što znači da daljnje promjene u ulazima ne utječu na zarobljeno stanje do sljedećeg ciklusa sata.Ova faza osigurava da flip-flop registrira ispravan ulaz bez utjecaja na sljedeće promjene tijekom istog ciklusa takta.

Nakon završetka glavne pozornice, pozornica robova dolazi u igru.U ovoj se fazi ažurira izlaz na temelju podataka koje je zabilježena glavna pozornica, ali samo na sljedećem rubu sata.Odvajanjem ulaznog hvatanja od izlaznog ažuriranja, stupanj slave osigurava da izlaz ostane stabilan sve dok matični stupanj nije u potpunosti obradio ulaz.To sprečava bilo kakve preuranjene ili nenamjerne promjene izlaza tijekom ciklusa sata.

Zašto je bitna konfiguracija glavnog slave?

Dvostupanjski postupak stabilizira rad JK Flip-Flop-a, sprečavajući neželjene oscilacije ili fluktuacije koje se mogu dogoditi u jednostavnijim konfiguracijama, posebno kada se oba ulaza drže visoka.Odvajanjem ulazne obrade od izlazne promjene, konfiguracija master-slave osigurava da izlazi ostaju predvidljivi i stabilni, čak i u situacijama kada je vrijeme vrijedno.

Obraćajući se utrci oko stanja u JK Flip-flops

Uvjeti u trci javljaju se u JK-flop-u, kada su oba ulaza, J i K, visoki, a signal sata ostaje aktivan predugo.To dovodi do kontinuiranog prebacivanja izlaza, što može uzrokovati pogrešno ponašanje i poremetiti pouzdanost kruga.

Postavljanje master-slave koristi dvostupanjski postupak za sprečavanje problema s utrkom.Glavna faza bilježi ulazne vrijednosti na rubu sata i zaključava ih. Slave faza ažurira izlaze na sljedećem rubu sata, osiguravajući da se izlaz ne promijeni dok se ulazi u potpunosti ne obrađuju.Ovaj pristup učinkovito sprječava da se izlaz nekontrolirano prebaci, čak i ako ulazi ostanu visoki duže vrijeme.

Druga metoda za izbjegavanje uvjeta u trci je podešavanje trajanja pulsa sata.Ako puls sata bude kraći od kašnjenja razmnožavanja Flip-Flopa, možete osigurati da se stanje ne promijeni više od jednom u istom ciklusu sata.To sprječava da se flip-flop više puta prebaci tijekom jednog ciklusa, stabilizirajući izlaz.

Dinamika prebacivanja u JK Flip-flops

Ponašanje prebacivanja JK Flip-Flop u velikoj mjeri pokreće se vremenom signala sata i ulaznim razinama (J i K).Flip-flop mijenja stanje na temelju uloga prisutnih na pozitivnom rubu signala sata.U ovom opasnom trenutku, Flip-Flop ocjenjuje ulaze i u skladu s tim ažurira svoj izlaz.

Kad signal sata udari u uspon, JK Flip-Flop čita trenutna stanja ulaza J i K.Ovisno o njihovim vrijednostima, flip-flop će ili držati, postaviti, resetirati ili prebaciti njegov izlaz.

Digitalni satovi: Točnost je sve u digitalnim satovima, a JK Flip-flops pomažu u održavanju ove preciznosti osiguravajući da se promjene stanja događaju samo u preciznim intervalima sata.

Sekvencijalni logički testeri: U sustavima koji testiraju funkcionalnost logičkih krugova, JK flip-flops igra ulogu u provjeri da li svaka komponenta ispravno reagira na određene vremenske signale.

Ostali vremenski osjetljivi sustavi: U raznim digitalnim aplikacijama u kojima je vrijeme rizično, poput komunikacijskih sustava ili jedinica za obradu podataka, JK Flip-FLOP osigurava da se prijelazi stanja događaju u sinkronizaciji sa satom, sprječavajući pogreške u vremenu.

Zaključak

JK Flip-Flop ističe se kao krajnji element u dizajnu digitalnog kruga, nudeći mješavinu svestrane i preciznosti očajnički za širok niz aplikacija u rasponu od pohrane memorije do podjele frekvencije i sinkronizacije digitalnih procesa.Njegova sposobnost ublažavanja uvjetima rase kroz inovativne konfiguracije, poput aranžmana master-slave, naglašava njegovu prilagodljivost u rješavanju inherentnih izazova dizajna.Jednako tako, ozbiljna uloga Flip-Flopa u osiguravanju preciznih prijelaza stanja naglašava njegovu potrebnu prirodu u stvaranju i održavanju pouzdanih i učinkovitih digitalnih sustava.Kako tehnologija napreduje, razvijajući se dizajni i primjene JK Flip-Flop-a i dalje su ključni u guranju granica digitalne elektronike prema sofisticiranijim i robusnijim arhitekturama.

Često postavljana pitanja [FAQ]

1. Koje su primjene JK Flip flopa?

JK Flip-Flop se intenzivno koristi u digitalnoj elektronici za različite zadatke:

Vremenske prijave: Može poslužiti kao element kašnjenja ili tajmer kada je spojen u određenim konfiguracijama.

Brojači i registri: Prebacivanjem svog stanja svakim pulsom sata koristi se za dizajniranje različitih brojača i registara pomaka koji su krajnji u sekvencijalnim logičkim krugovima.

Skladištenje memorije: Omogućuje osnovnu jedinicu memorije, korisno u pohranjivanju bitova u računalnim aplikacijama.

2. Kako JK Flip-Flop djeluje sa tablicom istine?

JK Flip-Flop ima dva ulaza (J i K) i signal sata.Njegov rad varira ovisno o ulaznim stanjima, sinkroniziranim na sat:

• J = 0, K = 0: Izlaz se ne mijenja.

• J = 0, K = 1: Izlaz se resetira na 0.

• J = 1, K = 0: Izlaz je postavljen na 1.

• J = 1, K = 1: Izlaz se prebacuje (tj. Ako je bio 0, postaje 1 i obrnuto).

3. Što je JK Flip flop i radi li?

JK Flip-flop kombinira svojstva SR i T-flops.Izbjegava "zabranjeno" stanje koje se vidi u SR flip-flops učinkovito koristeći JK ulaze:

Stanje flip-flopa kontroliraju ulazi J i K, koji određuju treba li izlaz držati, resetirati, postaviti ili prebaciti, sinkronizirati s rastućim ili padajućim rubom pulsa sata.

4. Koje su primjene zasuna i flip-flops?

Pohrana podataka: Zasuni i flip-flops ozbiljni su za pohranu podataka unutar registara i memorijskih nizova.

Odjel za frekvenciju: Koristi se u frekvencijskim razdjelnicima zbog njihove sposobnosti mijenjanja stanja na rubovima sata, prepolovljavajući frekvenciju sa svakom fazom u nizu.

Državni strojevi: Osnovno u dizajniranju strojeva konačnih stanja koji se koriste za implementaciju uzastopnih logičkih i upravljačkih krugova.

Depouncing: Koristi se za stabilizaciju signala iz mehaničkih prekidača i gumba, osiguravajući pojedinačne, čiste prijelaze.

5. Za što se koriste flip-flops?

Binarna pohrana: Svaki Flip-Flop pohranjuje jedan dio podataka, čineći ih građevnim blokovima za binarne uređaje za pohranu.

Razdjelnici satova: Oni podijele frekvenciju ulaznog sata s dvije, korisne u digitalnim satovima i vremenskim aplikacijama.

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

JRC4558 OP-AMP: Značajke, specifikacije i aplikacije

na 2024/09/18

330 ohma otpornika i kodova boja

na 2024/09/13

Popularni postovi

-

Što je GND u krugu?

na 1970/01/1 2953

-

Vodič za priključak RJ-45: RJ-45 kodovi u boji konektora, sheme ožičenja, R-J45 aplikacije, RJ-45 podatkovne liste

na 1970/01/1 2505

-

Vrste konektora vlakana: SC VS LC i LC vs MTP

na 1970/01/1 2095

-

Razumijevanje napona napajanja u elektronici VCC, VDD, VEE, VSS i GND

na 0400/11/9 1901

-

Usporedba između DB9 i RS232

na 1970/01/1 1767

-

Što je LR44 baterija?

Električna energija, ta sveprisutna sila, tiho prožima svaki aspekt našeg svakodnevnog života, od trivijalnih uređaja do medicinske opreme opasne po život, ona igra tihu ulogu.Međutim, uistinu shvatiti ovu energiju, posebno kako je pohraniti i učinkovito iznijeti, nije lak zadatak.Upravo će se u pozadini ovaj članak usredotočiti na vrstu baterije kovanica koja se može činiti beznačaj...na 1970/01/1 1715

-

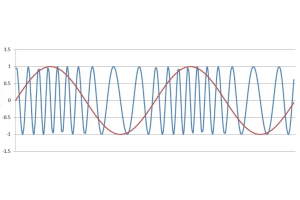

Razumijevanje osnovnih osnova: otpor induktivnosti i ikapacijacija

U zamršenom plesu elektrotehnike, trio temeljnih elemenata zauzima središnju pozornicu: induktivnost, otpor i kapacitet.Svaka nosi jedinstvene osobine koje diktiraju dinamičke ritmove elektroničkih krugova.Ovdje krećemo na put da dešifriramo složenost ovih komponenti, otkrivamo njihove različite uloge i praktične uporabe unutar ogromnog električnog orkestra.Induktivnost, sa svojim magnet...na 1970/01/1 1665

-

CR2430 Sveobuhvatni vodič za bateriju: Specifikacije, aplikacije i usporedba s baterijama CR2032

Što je CR2430 baterija?Prednosti CR2430 baterijaNormaCR2430 aplikacije za baterijeCr2430 ekvivalentCR2430 VS CR2032Baterija CR2430 VeličinaŠto potražiti prilikom kupovine CR2430 i ekvivalentaPodatkovni list pdfČesto postavljana pitanja Baterije su srce malih elektroničkih uređaja.Među mnogim dostupnim vrstama, kovanice igraju ključnu ulogu, koja se obično nalazi u kalkulatorima, daljinsk...na 1970/01/1 1571

-

Što je RF i zašto ga koristimo?

Tehnologija radiofrekvencije (RF) ključni je dio moderne bežične komunikacije, što omogućava prijenos podataka na velikim udaljenostima bez fizičkih veza.Ovaj članak ulazi u osnove RF -a, objašnjavajući kako elektromagnetsko zračenje (EMR) omogućuje RF komunikaciju.Istražit ćemo principe EMR-a, stvaranje i kontrola RF signala i njihove široke uporabe.Članak također obuhvaća povije...na 1970/01/1 1552

-

CR2450 VS CR2032: Može li se umjesto toga koristiti baterija?

Litijev manganski baterije imaju neke sličnosti s drugim litijevim baterijama.Visoka gustoća energije i dug radni vijek karakteristike su koje imaju zajedničke.Ova vrsta baterije osvojila je povjerenje i naklonost mnogih potrošača zbog svoje jedinstvene sigurnosti.Skupi tehnološki uređaji?Mali uređaji u našim domovima?Pogledajte oko sebe i vidjet ćete ih posvuda.Među mnogim litij-mangan...na 1970/01/1 1520