EP1C4F324C7N FPGA: podatkovni list, značajke, programiranje i specifikacije

Ovaj se vodič odnosi na EP1C4F324C7N, vrstu FPGA čipa koji je napravio Intel.Izvrsno je za projekte koji trebaju snažne performanse, ali također trebaju ostati unutar proračuna.U ovom ćete članku naučiti što ovaj čip može učiniti, kako funkcionira, gdje se koristi i kako ga programirati.Bilo da radite na elektronici za automobile, tvornice ili čak kućne uređaje, ovaj će vam vodič pomoći da shvatite zašto je EP1C4F324C7N pametan i fleksibilan izbor.Katalog

EP1C4F324C7N pregled

A Ep1c4f324c7n dio je Intelove serije Cyclone® FPGA, posebno dizajniranih za ekonomične aplikacije koje zahtijevaju dobru ravnotežu performansi i niske troškove.Ovaj FPGA sadrži 4.000 logičkih elemenata i 400 blokova logičkog niza (LABS), pružajući robusne mogućnosti za izradu umjerenih složenosti.Uključuje 76,5 kilobita ukupnog RAM -a i podržava do 249 I/O pinova, što ga čini vrlo svestranim za različite zahtjeve za povezivanjem.Rad na frekvencijama do 320 MHz i s rasponom napona napajanja od 1,425V do 1,575V, EP1C4F324C7N je opremljen za rukovanje zahtjevnim aplikacijama.Podržava širok raspon I/O standarda kao što su LVTTL, LVCMOS, SSTL-2 i SSTL-3, a kompatibilan je s vanjskim tipovima memorije poput DDR SDRAM-a, poboljšavajući njegovu korisnost u digitalnoj obradi signala, ugrađenom računarstvu i automatizacijskim sustavima.

Ako tražite da vaše operacije glatko rade s pouzdanom tehnologijom, postavljanje rasutih narudžbi ovog FPGA -e s nama može vam pomoći da osigurate da imate dostupnost i dosljednost koja vam je potrebna za vaše projekte.

EP1C4F324C7N CAD modeli

Ep1c4f324c7n simbol

EP1C4F324C7N

EP1C4F324C7N 3D model

Ep1c4f324c7n

• Logički elementi: FPGA sadrži 4.000 logičkih elemenata koji omogućuju učinkovito implementaciju složenih logičkih krugova i digitalnih funkcija.

• Logički blokovi (laboratoriji): Uključuje 400 laboratorija, koji su temeljni građevni blokovi za FPGA arhitekturu, što olakšava dizajn svestranih konfiguracija digitalne logike.

• Ukupni RAM komadići: FPGA je opremljen sa 76,5 kilobita ugrađenog RAM-a, pružajući resurse memorije na čipu za obradu i pohranu brzih podataka.

• Broj I/O igle: S 249 I/O PIN-a koji se mogu konfigurirati, EP1C4F324C7N podržava širok niz mogućnosti povezivanja, prilagodljivih različitim signalnim standardima i elektroničkim komponentama.

• Radna frekvencija: Može raditi na frekvencijama do 320 MHz, omogućujući mu da učinkovito postupa s računalnim zadacima i procesima.

• Napon za opskrbu: Uređaj djeluje u rasponu napona napajanja od 1,425V do 1,575V, osiguravajući fleksibilno i pouzdano upravljanje energijom u različitim aplikacijama.

• Petlje zaključane fazom (PLLS): Sadrži petlje za zaključavanje faza za precizno upravljanje satom za aplikacije osjetljive na tajming.

• Podrška za više I/O standarda: FPGA podržava različite I/O standarde kao što su LVTTL, LVCMOS, SSTL-2 i SSTL-3, što povećava njegovu kompatibilnost sa širokim rasponom elektroničkih komponenti i sustava.

EP1C4F324C7N blok dijagram

Dijagram ilustrira strukturu međusobne veze unutar FPGA, posebno referencirajući Ep1c4f324c7n Uređaj iz serije Altera Cyclone.U srži ovog izgleda su Blokovi logičkog niza (Laboratoriji), koji su vertikalno usklađeni moduli koji sadrže nakupine logičkih elemenata koji su odgovorni za implementaciju logičkih funkcija korisnika.Svaki je laboratorij povezan sa susjednim laboratorijima putem izravnih povezivanja, što omogućava brzu komunikaciju i minimiziranje kašnjenja širenja signala.Ove izravne veze pružaju učinkovit, lokalizirani prijenos podataka između susjednih logičkih blokova bez konzumiranja širih resursa usmjeravanja.

Oko Laboratorija su dvije glavne vrste globalnih međusobnih veza: redak međusobno povezivanje i Stupci međusobno povezani.Ove široke plave linije služe kao usmjeravanje autocesta, omogućujući signali da prelaze na veće dijelove tkanine FPGA.Redak međusobno povezuje horizontalno, dok stupac međusobno povezuje vertikalno.Oni olakšavaju vezu između udaljenih logičkih blokova i sučelja s ulaznim/izlaznim elementima ili drugim funkcionalnim jedinicama postavljenim preko čipa.

Lokalni međusobno povezivanje sjedi između laboratorija i služi kao prebacivanje tkanine koja s laboratorijima premošćuje globalne međusobne veze.Omogućuje logičkim blokovima da pristupe signalima i iz izravnih i globalnih međusobnih povezanosti.Ova hijerarhija usmjeravanja, kombinirajući izravne, lokalne, redak i stupce, pruža fleksibilan i skalabilan pristup distribuciji signala, optimizaciji performansi i korištenju logike unutar EP1C4F324C7N FPGA.

EP1C4F324C7N specifikacije

|

Tip |

Parametar |

|

Proizvođač |

Altera/Intel |

|

Niz |

Ciklon® |

|

Pakiranje |

Pladanj |

|

Status dijela |

Zastario |

|

Broj laboratorija/CLB -a |

400 |

|

Broj logičkih elemenata/stanica |

4000 |

|

Ukupni RAM komadići |

78.336 |

|

Broj I/O |

249 |

|

Napon - napad |

1.425V ~ 1.575V |

|

Montažni tip |

Površinski nosač |

|

Radna temperatura |

0 ° C ~ 85 ° C (TJ) |

|

Paket / slučaj |

324-bGa |

|

Paket uređaja dobavljača |

324-FBGA (19x19) |

|

Broj osnovnog proizvoda |

EP1C4 |

EP1C4F324C7N aplikacije

Umrežavanje opreme

EP1C4F324C7N vrlo je pogodan za upotrebu u mrežnim uređajima kao što su prekidači, usmjerivači i modemi.Pomaže učinkovito upravljanje podatkovnim prometom, poboljšavajući propusnost i smanjujući kašnjenje za održavanje mrežnih operacija visokih performansi.

Industrijska automatizacija

U području industrijske automatizacije, ovaj se FPGA može koristiti za kontrolu strojeva i robotskih sustava.Njegova sposobnost obrade složenih algoritama brzo omogućava kontrolu i nadzor, povećanje produktivnosti i sigurnosti u proizvodnim okruženjima.

Potrošačka elektronika

EP1C4F324C7N pronalazi aplikacije u potrošačkoj elektronici, posebno u pokretanju zaslona visoke rezolucije i upravljanju interaktivnim sučeljima u uređajima poput pametnih televizora i naprednih sustava za automatizaciju kućne automatizacije.Njegove robusne mogućnosti obrade osiguravaju glatka i reaktivna iskustva.

Automobilski sustavi

Unutar automobila, ovaj FPGA doprinosi funkcionalnosti sustava naprednih sustava za pomoć vozaču (ADAS) i infotainment sustava u vozilu.Podržava obradu i odlučivanje za sigurnosne i zabavne značajke u modernim vozilima.

Zrakoplovstvo i obrana

FPGA je primjenjiva i u zrakoplovnim i obrambenim sektorima, gdje upravlja zadacima obrade signala i slike za radarski i komunikacijski sustavi.Njegova visoka pouzdanost i sposobnost rada u ekstremnim uvjetima čine je idealnim za vojne i zrakoplovne primjene.

Ep1c4f324c7n slični dijelovi

EP1C4F324C7N KORAKA

1. Izrada dizajna: Započnite pisanjem dizajna pomoću jezika opisa hardvera, kao što su VHDL ili Verilog.Ovaj kôd definira logičku strukturu i funkciju vaše hardverske implementacije.Važno je točno prevesti svoju hardversku ideju u HDL kako bi se osiguralo da se FPGA ponaša kako se očekuje.Prije nego što nastavite s implementacijom hardvera, simulirajte svoj HDL kôd pomoću softvera za simulaciju.Ovaj korak testira logiku i funkcionalnost vašeg dizajna u virtualnom okruženju, omogućujući vam da identificirate i ispravite pogreške u ranom procesu razvoja.

2. Kompilacija i sinteza : Upotrijebite Altera's Quartus II softver za sastavljanje i sintetiziranje vašeg HDL koda.Kompilacija prevodi vaš HDL u netlist, generički opis FPGA hardvera koji preslikava vaš dizajn na logičke elemente i usmjeravanje resursa.Proces ugradnje, dio tijeka rada Quartus II, uključuje postavljanje i usmjeravanje vašeg dizajna u FPGA.Optimizira postavljanje logičkih elemenata i usmjeravanje veza kako bi se ispunili zahtjevi za izvedbu i umanjili upotrebu resursa.

3. PIN zadatak: Pinner PIN -a u Quartusu II omogućuje vam dodjeljivanje određenih igle na FPGA ulazima i izlazima definiranim u vašem HDL kodu.Pravilno dodjeljivanje PIN -a dobro je za fizičku povezanost i interakciju FPGA s drugim hardverskim komponentama u vašem sustavu.

4. Analiza vremena: Upotrijebite TIMEQUEST TIMING Analyzer kako biste osigurali da vaš dizajn ispunjava zahtjeve vremena.Ovaj alat provjerava vrijeme postavljanja i zadržavanja, te ukupne performanse vremena, pomažući u sprječavanju problema poput korupcije podataka i nestabilnosti sustava.

5. Generacija programiranja datoteka: Nakon što se dizajn sastavi, sintetizira i provjeri za vrijeme, koristite alat za montažu unutar Quartus II da biste generirali programsku datoteku.Ova datoteka, obično s .SOF (SRAM objektna datoteka) ili .POF (Programirajuća objektna datoteka) proširenje, sadrži podatke konfiguracije za FPGA.

6. Programiranje uređaja: Spojite ploču FPGA na svoje računalo pomoću JTAG sučelja, poput USB-Blaster-a.Ovo sučelje koristi se za prijenos programijske datoteke s računala na FPGA.Otvorite alat Quartus II programera za učitavanje i prijenos programijske datoteke na FPGA.Ovaj korak konfigurira FPGA s vašim dizajnom, u osnovi "programiranje" uređaja za obavljanje željenih funkcija.

7. Provjera: Jednom kada se FPGA programira, obavite funkcionalno testiranje kako biste provjerili da FPGA djeluje ispravno prema dizajnerskim specifikacijama.Ovo testiranje može uključivati testne slučajeve u laboratorijskom okruženju, provjeru operacija sučelja i osiguravanje FPGA ispravno komunicira s drugim hardverskim komponentama.

EP1C4F324C7N Prednosti

Fleksibilnost i rekonfigurabilnost

EP1C4F324C7N nudi neusporedivu fleksibilnost u usporedbi s mikrokontrolerima i ASIC -ovima, koji su fiksirani u njihovoj funkciji jednom proizvedeni.Ovaj FPGA može se reprogramirati kako bi se prilagodio novim zahtjevima ili promjenama u dizajnu sustava za aplikacije koje se vremenom razvijaju.Ova rekonfigurabilnost omogućuje ažuriranje svojih sustava bez zamjene hardvera, smanjujući vrijeme troškova i razvoja.

Paralelne mogućnosti obrade

Svojom sposobnošću istodobno izvršavanja više operacija, EP1C4F324C7N izvrsno je u okruženjima koja zahtijevaju računanje visokih performansi.Ova paralelna sposobnost obrade prednost je u odnosu na tradicionalne mikrokontrolere koji rade uzastopno, što FPGA čini prikladnijim za intenzivnije aplikacije kao što su digitalna obrada signala, video obrada i složeni upravljački sustavi.

Prilagođena implementacija hardvera

FPGA omogućava dizajn prilagođene hardverske logike prilagođene posebno operativnim potrebama korisnika.To znači da se EP1C4F324C7N može optimizirati za obavljanje određenih zadataka učinkovitije od standardnih procesora ili ASIC -a, pružajući vrhunske performanse i učinkovitost snage za specijalizirane aplikacije.

Isplativost za proizvodnju niske do srednjeg volumena

Za projekte u kojima količina proizvodnje ne opravdava visoke troškove razvoja ASIC-a, EP1C4F324C7N predstavlja ekonomičnu alternativu.Pruža prednosti prilagođenog hardvera bez značajnih unaprijed ulaganja potrebnih za ASIC dizajn i proizvodnju, što ga čini idealnim za prototipove, male i srednje projekte ili specijalizirane industrijske aplikacije.

Integracija i učinkovitost prostora

Sposobnost integriranja više funkcija i komponenti u jedan FPGA čip čini EP1C4F324C7N visoko vrijednim u aplikacijama ograničenim prostorom.Ova integracija dovodi do manjih, kompaktnijih dizajna uređaja, izvrsnog u prijenosnom elektroniku, automobilskim aplikacijama i drugim scenarijima u kojima je potrebna učinkovitost prostora.

EP1C4F324C7N dimenzije pakiranja

• Vrsta paketa: 324-pinski niz finih pitki

• Veličina paketa (Duljina x širina): 19 mm x 19 mm

• Maksimalna sjedeća visina: 3,5 mm

• Terminal: 1 mm

EP1C4F324C7N Proizvođač

EP1C4F324C7N je terenski programabilni niz vrata (FPGA) proizveden Inteliran, nakon njihovog stjecanja Altera.Kao dio Intelove serije Cyclone®, ovaj FPGA predstavlja segment Intelovog širokog portfelja integriranih tehnoloških rješenja.Intel, lider u industriji poluvodiča, integrira napredne proizvodne tehnologije i opsežnu podršku za pružanje robusnih FPGA rješenja, uključujući EP1C4F324C7N, koji sadrži složene logičke sposobnosti u kompaktnom faktoru oblika.Ovaj FPGA ističe Intelovu posvećenost pružanju računalnih komponenti visokih performansi koje zadovoljavaju različite tehnološke potrebe.

Zaključak

Bilo da razvijate li logiku prilagođene kontrole, izgradnju komunikacijskih sustava velike brzine ili prototipiranje specijaliziranih digitalnih funkcija, EP1C4F324C7N FPGA pruža optimalnu ravnotežu performansi, fleksibilnosti i troškova.Sa svojom širokom I/O kompatibilnošću, integriranom memorijom i učinkovitom rekonfigurabilnošću, on podržava skalabilne i svemirno učinkovite dizajne u širokom rasponu modernih aplikacija.Podržana Intelovom vodećom podrškom, ovaj FPGA ostaje pouzdano i prilagodljivo rješenje za traženje robusne programabilne logike i u implementaciji s malim i srednjim količinama.

Podatkovni list pdf

EP1C4F324C7N podataka:

Sav dev pkg chg 1/kolovoz/2018.pdf

Multi Dev dessicant CHG 19/srp/2019.pdf

Više serija softvera chgs 26/ožujak/2020.pdf

Virtual JTAG megafuntion vodič.pdf

Cilindrični držači baterija.pdf

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

Često postavljana pitanja [FAQ]

1. Može li se EP1C4F324C7N koristiti s DDR ili SDRAM?

Da, ovaj FPGA podržava tipove vanjske memorije, uključujući DDR SDRAM, zahvaljujući multi-standardnom I/O podršci.Međutim, vaš PCB izgled mora se pridržavati strogih smjernica vremena i impedancije za povezivanje memorije velike brzine.

2. Koji su tipični zahtjevi za napajanje za EP1C4F324C7N?

Ovaj uređaj radi na 1,425V do 1,575V napona jezgre, s dodatnim naponima potrebnim za I/O standarde.Za precizno planiranje energije, koristite Intelov analizator PowerPlay Power u Quartusu za procjenu potrošnje na temelju vašeg dizajna.

3. Je li EP1C4F324C7N ROHS CompunInt i bez olova?

Da, EP1C4F324C7N je u skladu s ROHS direktivama i dostupan je u paketima bez olova.To ga čini prikladnim za ekološki regulirana tržišta i aplikacije koje zahtijevaju certificiranje zelene elektronike.

4. Koliko je potrebno sastaviti i programirati dizajn na EP1C4F324C7N?

Za umjerene dizajne složenosti, kompilacija i programiranje obično traju 3 do 5 minuta, ovisno o performansama vašeg računala.Analiza vremena i zadatke PIN -a mogu proširiti postupak ako vaš dizajn zahtijeva strogo ograničenje vremena.

5. Trebam li neki posebni alati za programiranje EP1C4F324C7N?

Trebat će vam Intelov softver Quartus II, koji je dostupan u besplatnom lite izdanju, i USB-Blaster ili kompatibilnom JTAG programeru.Ovi alati omogućuju vam sastavljanje dizajna, generiranje programskih datoteka i prenošenje na FPGA.

GC5330IZEV procesor digitalnog signala: značajke, aplikacije, alternative i specifikacije

na 2025/04/1

Kompletni vodič za otpornik 0402: Specifikacije, aplikacije i tehnike lemljenja

na 2025/04/1

Popularni postovi

-

Složeni računali s uputama: Kako su promijenili računanje?

na 8000/04/18 147766

-

USB-C pinout i značajke

na 2000/04/18 111994

-

Korištenje Xilinx Unified simulacijski primitivi: sveobuhvatni vodič za dizajn i simulaciju FPGA

na 1600/04/18 111351

-

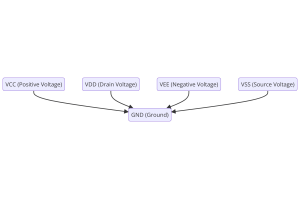

Naponi napajanja u elektronici: Značenje VCC, VDD, VEE, VSS i GND

na 0400/04/18 83755

-

RJ45 Vodič za priključak: pinout, ožičenje, vrste kabela i upotreba

na 1970/01/1 79550

-

Krajnji vodič za kodove u boji žice u modernim električnim sustavima

Način na koji naši električni sustavi koriste boje nisu samo za izgled.Svaka boja žice sada označava određenu funkciju, što olakšava prepoznavanje i ispravno obradu električnih komponenti tijekom u...na 1970/01/1 66951

-

Vodič za čišćenje ventila: Funkcija, simptomi, testiranje i zamjena za optimalne performanse motora

Ventil za čišćenje ključni je dio sustava automobila koji pomaže u održavanju zraka čistim upravljanjem parima goriva prije nego što mogu pobjeći u atmosferu.To ne samo da pomaže okolišu smanjenjem...na 1970/01/1 63094

-

Kvaliteta (q) Faktor: jednadžbe i aplikacije

Faktor kvalitete, ili 'q', važan je prilikom provjere koliko dobro induktori i rezonatori rade u elektroničkim sustavima koji koriste radio frekvencije (RF).'Q' mjeri koliko dobro krug minimizira g...na 1970/01/1 63028

-

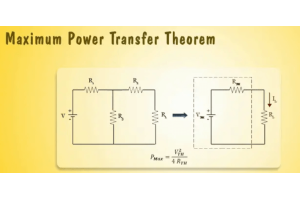

Postizanje vršnih performansi s maksimalnim teoremom prijenosa snage

Teorem maksimalnog prijenosa napajanja objašnjava kako energija iz izvora, poput baterije ili generatora, teče do povezanog opterećenja.Pokazuje točan uvjet u kojem opterećenje prima najviše snage....na 1970/01/1 54094

-

Specifikacije i kompatibilnost A23

A23 baterija je mala baterija u obliku cilindra s visokim naponom.Također se naziva 23A, 23AE ili MN21, radi na 12 volti i mnogo više od AA ili AAA baterija.Njegov poseban dizajn čini ga s...na 1970/01/1 52176