EPM3256AFC256-7 CPLD pregled: Značajke, pinout, programiranje i aplikacije

U ovom ćete vodiču potpuno pogledati EPM3256AFC256-7, CPLD visoke gustoće iz ALTERA-ove obitelji Max 3000A.Naučit ćete što je to, kako je izgrađen i što ga čini korisnim za različite digitalne dizajne.Prošetat ćemo kroz njegov izgled PIN -a, CAD modele, ključne značajke, unutarnju strukturu, ponašanje snage i detalje o paketu.Također ćete vidjeti njegove aplikacije, kako ih programirati putem JTAG -a, kako se uspoređuje sa sličnim dijelovima i prednosti i nedostataka.Katalog

Što je EPM3256AFC256-7?

A EPM3256AFC256-7 je CPLD visoke gustoće (složeni programabilni logički uređaj) iz Altera Max 3000A obitelji, dizajniran za brzu, pouzdanu i nehlapljivu logičku implementaciju.Koristi EEPROM tehnologiju, omogućavajući uređaju da zadržava svoju konfiguraciju bez vanjske memorije, što ga čini idealnim za stabilnu, dugoročnu upotrebu.Pripadajući seriji EPM3xxx, dijeli zajedničku programabilnu interkonekciju i arhitekturu Macrocell, nudeći različite logičke gustoće kroz varijante poput EPM3032A, EPM3064A, EPM3128A i EPM3512A.Kao dio dokazane naslijeđene linije, ostaje cijenjena u mnogim dizajnima unatoč zastarjelom statusu.

Tražite EPM3256AFC256-7?Kontaktirajte nas kako biste provjerili trenutne zalihe, vrijeme i cijene.

EPM3256AFC256-7 PING DIJAGRAM

Dijagram pribavljanja EPM3256AFC256-7 (sličan onome prikazanom za EPM3512A) ilustrira izgled fizičke kuglice i orijentaciju BGA paketa uređaja.S lijeve strane, crna točka označava mjesto A1 A1, koja služi kao orijentacijska referenca za pravilno poravnavanje tijekom postavljanja PCB -a i lemljenja.S desne strane, rešetka prikazuje matricu kuglice s oznakom slovima (redovi A - T) i brojevima (stupci 1–16), formirajući koordinatni sustav za precizno identificiranje svakog signala ili lopte za napajanje.Ovaj izgled osigurava precizno preslikavanje između unutarnje logike čipa i vanjskih igara, omogućujući ispravno usmjeravanje signala, snage i prizemnih veza na PCB -u.

EPM3256AFC256-7 CAD modeli

EPM3256AFC256-7 simbol

EPM3256AFC256-7

EPM3256AFC256-7 3D model

EPM3256AFC256-7

• Nehlapljiva arhitektura koja se temelji na EEPROM

Uređaj koristi EEPROM ćelije za pohranjivanje podataka o konfiguraciji, omogućujući mu da zadrži svoju programiranu logiku čak i kad se isključi.Za razliku od FPGA-a sa sjedištem u SRAM-u, pri pokretanju ne treba vanjski konfiguracijski uređaj, što pojednostavljuje dizajn ploče i smanjuje troškove sustava.

• 256 makrocela i 16 laboratorija

Pruža 256 programabilnih makrocela organiziranih u 16 blokova logičkog niza (LABS), što daje dovoljno kapaciteta za implementaciju složenih logičkih funkcija.Svaka makrocell podržava i kombinatorne i registrirane načine, što ga čini fleksibilnim za različite logičke strukture.

• Približno.5.000 upotrebnih vrata

S oko 5000 ekvivalenta vrata, uređaj može zamijeniti više TTL ili PAL uređaja u jednom čipu.Ova konsolidacija smanjuje prostor ploče, međusobno povezivanje složenosti i poboljšava ukupnu pouzdanost sustava.

• Rad velike brzine (7,5 NS TPD)

Uređaj podržava brzo kašnjenje širenja od približno 7,5 ns i kašnjenja od sata do izlaza od oko 4,8 ns.Ova izvedba omogućuje pouzdanu primjenu visokofrekventnih dizajna do oko 126 MHz, ovisno o aplikaciji.

• U sustavu programabilno putem JTAG-a

EPM3256AFC256-7 podržava programiranje kroz standardno IEEE 1149.1 JTAG sučelje, omogućujući konfiguraciju bez uklanjanja čipa s PCB-a.To pojednostavljuje razvoj, uklanjanje pogrešaka i nadogradnje na terenu.

• Multivolt i/o podrška

Njegovi I/O PIN -ovi podržavaju više razina napona, uključujući rad 2,5 V i 3,3 V, dok su ulazi tolerantni do 5 V. To omogućava uređaju da se sučelja s širokim brojem naslijeđa i modernih logičkih obitelji bez miješača razine.

• Do 161 korisnika I/O igle

CHIP nudi veliki broj I/O igle pristupačnih korisnika, pružajući fleksibilnost za široka sabirna sučelja ili više kontrolnih signala.I/O struktura podržava kontrolu brzine i izlaze otvorenih odvajanja za smanjenje buke i primjenu sabirnice.

• Kontrola i optimizacija snage

Svaki izlaz može se konfigurirati za brzi ili spor brzina uravnoteženja brzine s integritetom signala.Uz to, makrocele mogu se pojedinačno postaviti na način male snage na nekritičnim stazama, smanjujući ukupnu potrošnju energije uređaja.

• Unutarnje programiranje generacije napona

Uređaj interno generira vlastiti programski naponi, uklanjajući potrebu za vanjskim zalihama visokog napona tijekom programiranja.Ova značajka pojednostavljuje dizajn snage ploče i poboljšava praktičnost programiranja.

• Zaštita bita sigurnosti

Programirani sigurnosni bit može se postaviti kako bi se spriječilo neovlašteno čitanje sadržaja uređaja.Ova značajka štiti intelektualno vlasništvo i pomaže u održavanju sigurnosti vlasničkih dizajna.

• TTL/CMOS kompatibilnost

CPLD se može izravno sučeljavati sa standardnim razinama logike TTL i CMOS.Ova kompatibilnost olakšava integriranje u postojeće sustave i zamjenu starijih programibilnih logičkih uređaja bez većih redizajna.

• Deterministička izvedba vremena

Unutarnja struktura usmjeravanja pruža predvidljiva kašnjenja, omogućujući precizno analizu vremena najgoreg slučaja tijekom razvoja.Zbog toga je uređaj vrlo prikladnim za vremenski kritično-kritičku logiku kontrole i sučelja.

Max 3000a blok dijagram

Dijagram Bloka Max 3000A ilustrira unutarnju strukturu koja definira kako se logika implementira unutar uređaja poput EPM3256AFC256-7.U jezgri je programabilni interkonekcijski niz (PIA), koji povezuje blokove s više logičkih nizova (laboratorij), od kojih svaki sadrži nekoliko makrocela za izgradnju kombinacijske i uzastopne logike.Oko Laboratorija su I/O upravljački blokovi koji upravljaju interakcijom između unutarnje logike i vanjskih igara, podržavajući značajke poput izlaza i globalnih kontrolnih signala.Ova organizirana arhitektura omogućava uređaju da učinkovito implementira složene digitalne funkcije s predvidljivim vremenom i fleksibilnim usmjeravanjem, što ga čini idealnim za kontrolne logike, logike ljepljenja i zadataka integracije sustava.

ICC nasuprot frekvenciji za Max 3000A uređaje

Grafikon pokazuje kako aktivna struja opskrbe Max 3000A uređaja poput EPM3256AFC256-7 varira s radnom frekvencijom na 3,3 V i sobnoj temperaturi.Istaknuta su dva načina rada: mala snaga, što smanjuje potrošnju struje na nižim frekvencijama i veliku brzinu, što podržava veće frekvencije, ali zahtijeva više struje.Kako se frekvencija povećava, aktivna struja raste, dosežući oko 172 Ma pri 172,4 MHz u načinu velike brzine i oko 102 mA pri 102 MHz u načinu male snage.Ovaj je odnos važan za proračun napajanja i toplinski dizajn, pomažući vam da odaberete pravu ravnotežu između performansi i energetske učinkovitosti za njihove primjene.

EPM3256AFC256-7 Specifikacije

|

Tip |

Parametar |

|

Proizvođač |

Altera/Intel |

|

Niz |

Max® 3000a |

|

Pakiranje |

Pladanj |

|

Status dijela |

Zastario |

|

Programirajuća vrsta |

U sustavu programibilno |

|

Vrijeme odgode tpd (1) max |

7,5 ns |

|

Napon napona - unutarnji |

3 V ~ 3,6 V |

|

Broj logičkih elemenata/blokova |

16 |

|

Broj makrocela |

256 |

|

Broj vrata |

5000 |

|

Broj I/O |

161 |

|

Radna temperatura |

0 ° C ~ 70 ° C (TA) |

|

Montažni tip |

Površinski nosač |

|

Paket / slučaj |

256-bga |

|

Paket uređaja dobavljača |

256-FBGA (17 × 17) |

|

Broj osnovnog proizvoda |

EPM3256 |

EPM3256AFC256-7

1. Logika ljepila i prijevod signala

EPM3256AFC256-7 široko se koristi kao logika ljepila za povezivanje različitih digitalnih komponenti unutar sustava.Može izvršiti dekodiranje adresa, multipleksiranje podataka ili premošćivanje protokola između podsustava koji djeluju na različitim razinama napona ili vremenskim domenama.Konsolidiranjem više diskretnih logičkih IC -a u jedan CPLD, on pojednostavljuje izgled PCB -a, smanjuje broj dijelova i poboljšava pouzdanost sustava.

2. Državni strojevi i kontrolna logika

Uređaj je idealan za implementaciju prilagođenih stanja strojeva koji kontroliraju sekvence, vrijeme i koordinaciju između komponenata sustava.Njegova predvidljiva vremenska i nehlapljiva konfiguracija čine je dobro prikladnima za kontrolne funkcije kao što su rutine inicijalizacije, upravljanje resetiranjem ili kontrola operativnog načina rada.To omogućava prebacivanje kontrolne logike mikrokontrolera ili ASIC -a, poboljšavajući ukupne performanse sustava.

3. Autobusna sučelja i periferni omoti

Sa svojim velikim brojem I/O igle i fleksibilnom logičkom strukturom, CPLD je izvrstan za stvaranje sučelja sabirnice, perifernog ljepila i pretvarača protokola.Može upravljati prijenosom podataka, arbitražom i sinkronizacijom između procesora, sjećanja ili vanjskih uređaja.Ova je sposobnost vrijedna u mješovito-tehnološkim sustavima u kojima različiti sabirnici ili signalni standardi moraju neprimjetno komunicirati.

4. industrijski i potrošački elektronički sustavi

EPM3256AFC256-7 obično se nalazi u automatizacijskim kontrolerima, telekom opremi, medicinskim uređajima i drugim ugrađenim platformama koje zahtijevaju umjerenu logičku gustoću.Njegova pouzdana nehlapljiva konfiguracija, rad male snage i programiranje u sustavu čini je dobro za dugotrajne, stabilne aplikacije.Mnogi imaju koristi od njegove sposobnosti za implementaciju prilagođenih logičkih funkcija bez redizajniranja hardvera, što omogućava fleksibilne nadogradnje sustava.

EPM3256AFC256-7 Slični dijelovi

|

Specifikacija |

EPM3256AFC256-7 |

EPM3256AFI256-10 |

EPM3256AQC208-7N |

EPM3256AQC208-7 |

EPM3256AFC256-10 |

EPM3256AQI-10N |

|

Obitelj uređaja |

Max 3000a |

Max 3000a |

Max 3000a |

Max 3000a |

Max 3000a |

Max 3000a |

|

Logički kapacitet (makrocele) |

256 |

256 |

256 |

256 |

256 |

256 |

|

Ekvivalent vrata |

~ 5.000 |

~ 5.000 |

~ 5.000 |

~ 5.000 |

~ 5.000 |

~ 5.000 |

|

Vrsta paketa |

FBGA (fini pitch) |

FBGA (fini pitch) |

QFP 208-pin |

QFP 208-pin |

FBGA (fini pitch) |

QFP / Slično |

|

Broj |

256 |

256 |

208 |

208 |

256 |

208 |

|

Brzina brzina |

-7 |

-10 |

-7 |

-7 |

-10 |

-10 |

|

Napon napajanja (VCC) |

3.0 - 3.6 V |

3.0 - 3.6 V |

3.0 - 3.6 V |

3.0 - 3.6 V |

3.0 - 3.6 V |

3.0 - 3.6 V |

|

I/O Broj |

Do 161 |

Do 161 |

Nešto manje (QFP) |

Nešto manje (QFP) |

Do 161 |

Malo manje |

|

Radna temperatura |

0 ° C do +70 ° C |

0 ° C do +70 ° C |

0 ° C do +70 ° C |

0 ° C do +70 ° C |

0 ° C do +70 ° C |

0 ° C do +70 ° C |

|

Fokus aplikacije |

Uravnotežena brzina i I/O |

Varijanta veće brzine |

Kompaktni izgled ploče |

Ne-rohs varijanta |

Brže u istom pkg |

Alt.Paket za naslijeđene sustave |

EPM3256AFC256-7 Koraci programiranja

Prije nego što možete upotrijebiti EPM3256AFC256-7, morate učitati svoj prilagođeni logički dizajn u uređaj putem njegovog JTAG sučelja.Ovaj postupak osigurava da je CPLD pravilno konfiguriran i spreman za obavljanje svojih predviđenih funkcija u vašem sustavu.

1.

Započinjete stvaranjem dizajna pomoću alata za razvoj poput Intel Quartus.To uključuje pisanje HDL koda ili sheme crtanja, dodjeljivanje I/O pinova i postavljanje ograničenja vremena.Nakon završetka, sastavljate projekt za generiranje programskih datoteka (obično .POF ili .JAM) koja sadrži sve podatke konfiguracije potrebne za CPLD.

2. Povežite JTAG programera i hardver

Zatim napajate ploču odgovarajućim razinama napona i spojite JTAG kabel (npr. USB-Blaster) na JTAG zaglavlje uređaja.Provjerite jesu li TCK, TMS, TDI i TDO igle ispravno ožičeni kako bi se izbjegle komunikacijske pogreške.Potrebni su stabilan napajanje i ispravna orijentacija kabela kako bi se osiguralo glatko programiranje.

3. Odaberite uređaj i učitajte datoteku programiranja

U svom softveru za programiranje otkrivate lanac JTAG i provjerite da li se EPM3256AFC256-7 pojavljuje ispravno.Zatim učitate sastavljenu programirajuću datoteku i odaberete odgovarajuće operacije kao što su program, konfigurirajte i provjerite.Ovaj korak osigurava da alat točno zna koju datoteku za učitavanje i kako programirati ciljni uređaj.

4. Izbrišite, programirajte i provjerite uređaj

Softver prvo briše bilo koju postojeću konfiguraciju unutar nehlapljive memorije CPLD-a.Zatim piše novu logičku konfiguraciju u uređaj i izvodi korak provjere za potvrdu uspješnog programiranja.To osigurava da unutarnji EEPROM sada sadrži vaš točan dizajn i zadržat će ga čak i kad se ukloni snaga.

5. Izvršite provjere nakon programiranja

Nakon programiranja testirate uređaj primjenom ulaznih signala i provjerom da se izlazi ponašaju kako se očekuje.Također biste trebali provjeriti ima li sukoba PIN -a ili netočnog usmjeravanja koji bi mogli utjecati na funkcionalnost.Ako se pojave bilo kakve probleme, lako možete reprogramirati CPLD putem JTAG -a bez uklanjanja s PCB -a.

EPM3256AFC256-7 Prednosti i nedostaci

Prednosti

• Počinje raditi odmah pri napajanju bez vanjske konfiguracije.

• Nudi stabilno i predvidljivo vrijeme za pouzdane dizajne.

• Konzuze manje statičke snage od većih FPGA -ova.

• snižava ukupne troškove sustava i pojednostavljuje dizajn ploče.

• Jednostavno reprogramiranje i uklanjanje pogrešaka izravno u sustavu.

Nedostaci

• Ograničeni logički kapacitet za velike ili složene dizajne.

• Niže maksimalne performanse u usporedbi s modernim uređajima.

• Rizik od zastarjelosti i ograničena dugoročna dostupnost.

• Nedostaju napredne značajke pronađene u novijoj programibilnoj logici.

• Manje skalabilno za buduća ekspanzija dizajna.

EPM3256AFC256-7 Dimenzije pakiranja

|

Tip |

Parametar |

|

Vrsta paketa |

256-FBGA (niz rešetke s finim pitch) |

|

Veličina paketa (d × e) |

17,00 mm × 17,00 mm (bsc) |

|

Maksimalna visina paketa (a) |

2,60 mm |

|

Visina suprotstavljanja / lopte (A1) |

0,35 mm (minimalno) |

|

Kuglica (e) kuglica (e) |

1,00 mm (nominalno) |

|

Promjer kuglice (b) |

0,50 mm - 0,60 mm (tipično) |

|

Koplanarnost (maksimalno) |

0,20 mm |

|

Montažni tip |

Površinski nosač |

|

Paket uređaja dobavljača |

256-FBGA (17 × 17) |

EPM3256AFC256-7 Proizvođač

EPM3256AFC256-7 proizvodi Alter, pionir u programibilnoj tehnologiji logičkih uređaja.Altera je postala široko poznata po svojim CPLD -ovima i FPGAS -u, koji su postavljali industrijske standarde za performanse, fleksibilnost i integraciju.U 2015. godini, Inteliran Stečena Altera, a uređaj je sada dio Intelove grupe programabilnih rješenja, osiguravajući stalnu podršku i integraciju unutar Intelovog ekosustava proizvoda.

Zaključak

EPM3256AFC256-7 ističe se za svoju nehlapljivu arhitekturu koja se temelji na EEPROM-u, brze vremenske performanse i fleksibilne I/O mogućnosti, što ga čini pouzdanim izborom za kontrolnu logiku, logiku ljepila i sabiranje sabirnica u ugrađenim i industrijskim sustavima.Njegovo determinističko ponašanje, programabilnost u sustavu i podrška za višenapon pojednostavljuju dizajnersku integraciju i održavanje.Iako nudi umjerenu logičku sposobnost i suočava se s zastarjelom u usporedbi s modernim alternativama, njegova pouzdanost i jednostavnost upotrebe držali su je relevantnim u mnogim stabilnim aplikacijama za dugoročno-lifecycle.

Podatkovni list pdf

EPM3256AFC256-7 podatkovnice:

O nama

ALLELCO LIMITED

Čitaj više

Brz upit

Molimo pošaljite upit, odmah ćemo odgovoriti.

Često postavljana pitanja [FAQ]

1. Može li EPM3256AFC256-7 u mom dizajnu zamijeniti starije TTL ili PAL logičke uređaje?

Da.S približno 5000 upotrebljivih vrata i kompatibilnošću TTL/CMOS, EPM3256AFC256-7 može zamijeniti više diskretnih TTL-a ili PAL IC-a, smanjujući prostor ploče i pojednostavljujući usmjeravanje uz poboljšanje pouzdanosti.

2. Da li EPM3256AFC256-7 zahtijeva vanjsku konfiguracijsku memoriju?

Ne. Koristi EEPROM tehnologiju, tako da se konfiguracija pohranjuje interno i automatski se učitava pri napajanju.Ovo uklanja potrebu za bilo kojim vanjskim konfiguracijskim uređajem, pojednostavljujući dizajn vaše ploče.

3. Kako se EPM3256AFC256-7 bavi okruženjima mješovitih napona?

Njegovi I/O PIN -ovi podržavaju 2,5 V i 3.3 V, s ulazom tolerantnim do 5 V. To vam omogućuje da ga povežete izravno i s naslijeđenim i modernim logičkim razinama bez potrebe za mijenjačima vanjske razine.

4. Koji se programer preporučuje za EPM3256AFC256-7?

Uređaj podržava programiranje u sustavu kroz standardno IEEE 1149.1 JTAG sučelje.INTELOVI USB-Blaster ili ekvivalentni JTAG programeri obično se koriste.

5. Kako se EPM3256AFC256-7 uspoređuje s modernim FPGAS-om?

Za razliku od modernih FPGA-ova koji se oslanjaju na vanjsku memoriju, EPM3256AFC256-7 interno pohranjuje konfiguraciju.Jednostavnije je, odmah troši manje snage i čizme, iako ima niži kapacitet i brzinu u usporedbi s današnjim uređajima.

XC2C256-7TQ144C CPLD: PINKOUT, značajke, vodič za programiranje i podatkovni list

na 2025/10/3

EP1C4F400C8 FPGA: Značajke, specifikacije, programiranje i alternative

na 2025/10/2

Popularni postovi

-

Složeni računali s uputama: Kako su promijenili računanje?

na 8000/04/18 147749

-

USB-C pinout i značajke

na 2000/04/18 111909

-

Korištenje Xilinx Unified simulacijski primitivi: sveobuhvatni vodič za dizajn i simulaciju FPGA

na 1600/04/18 111349

-

Naponi napajanja u elektronici: Značenje VCC, VDD, VEE, VSS i GND

na 0400/04/18 83714

-

RJ45 Vodič za priključak: pinout, ožičenje, vrste kabela i upotreba

na 1970/01/1 79502

-

Krajnji vodič za kodove u boji žice u modernim električnim sustavima

Način na koji naši električni sustavi koriste boje nisu samo za izgled.Svaka boja žice sada označava određenu funkciju, što olakšava prepoznavanje i ispravno obradu električnih komponenti tijekom u...na 1970/01/1 66871

-

Kvaliteta (q) Faktor: jednadžbe i aplikacije

Faktor kvalitete, ili 'q', važan je prilikom provjere koliko dobro induktori i rezonatori rade u elektroničkim sustavima koji koriste radio frekvencije (RF).'Q' mjeri koliko dobro krug minimizira g...na 1970/01/1 63005

-

Vodič za čišćenje ventila: Funkcija, simptomi, testiranje i zamjena za optimalne performanse motora

Ventil za čišćenje ključni je dio sustava automobila koji pomaže u održavanju zraka čistim upravljanjem parima goriva prije nego što mogu pobjeći u atmosferu.To ne samo da pomaže okolišu smanjenjem...na 1970/01/1 62948

-

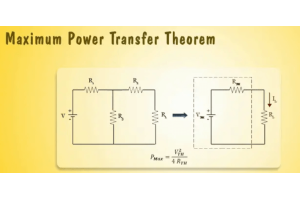

Postizanje vršnih performansi s maksimalnim teoremom prijenosa snage

Teorem maksimalnog prijenosa napajanja objašnjava kako energija iz izvora, poput baterije ili generatora, teče do povezanog opterećenja.Pokazuje točan uvjet u kojem opterećenje prima najviše snage....na 1970/01/1 54077

-

Specifikacije i kompatibilnost A23

A23 baterija je mala baterija u obliku cilindra s visokim naponom.Također se naziva 23A, 23AE ili MN21, radi na 12 volti i mnogo više od AA ili AAA baterija.Njegov poseban dizajn čini ga s...na 1970/01/1 52089